4-10 Computer Group Literature Center Web Site

Programming Details

4

Note The TEA* signal is not used at all by the MTX series. The

following table summarizes how the hardware errors are handled

by the MTX series:

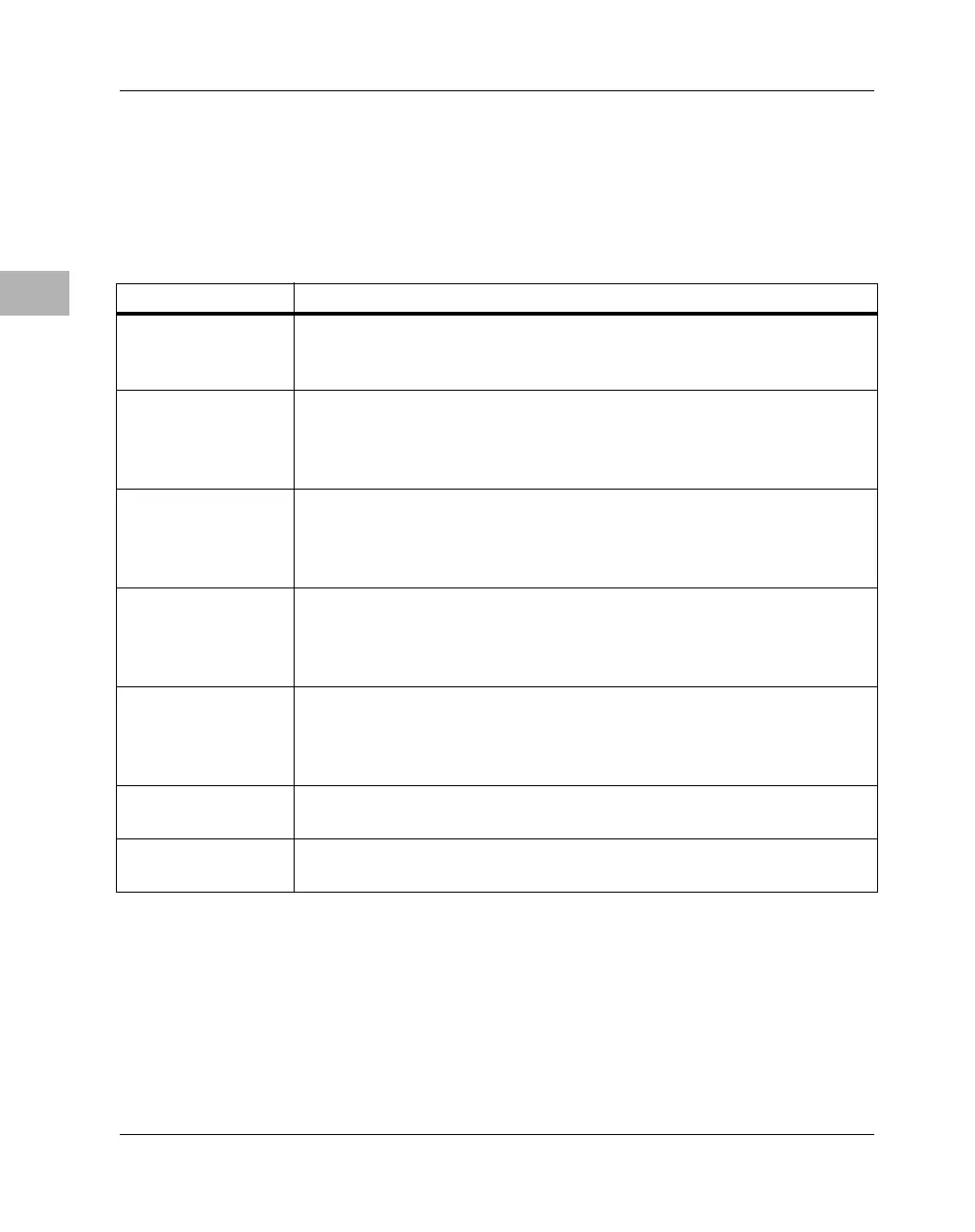

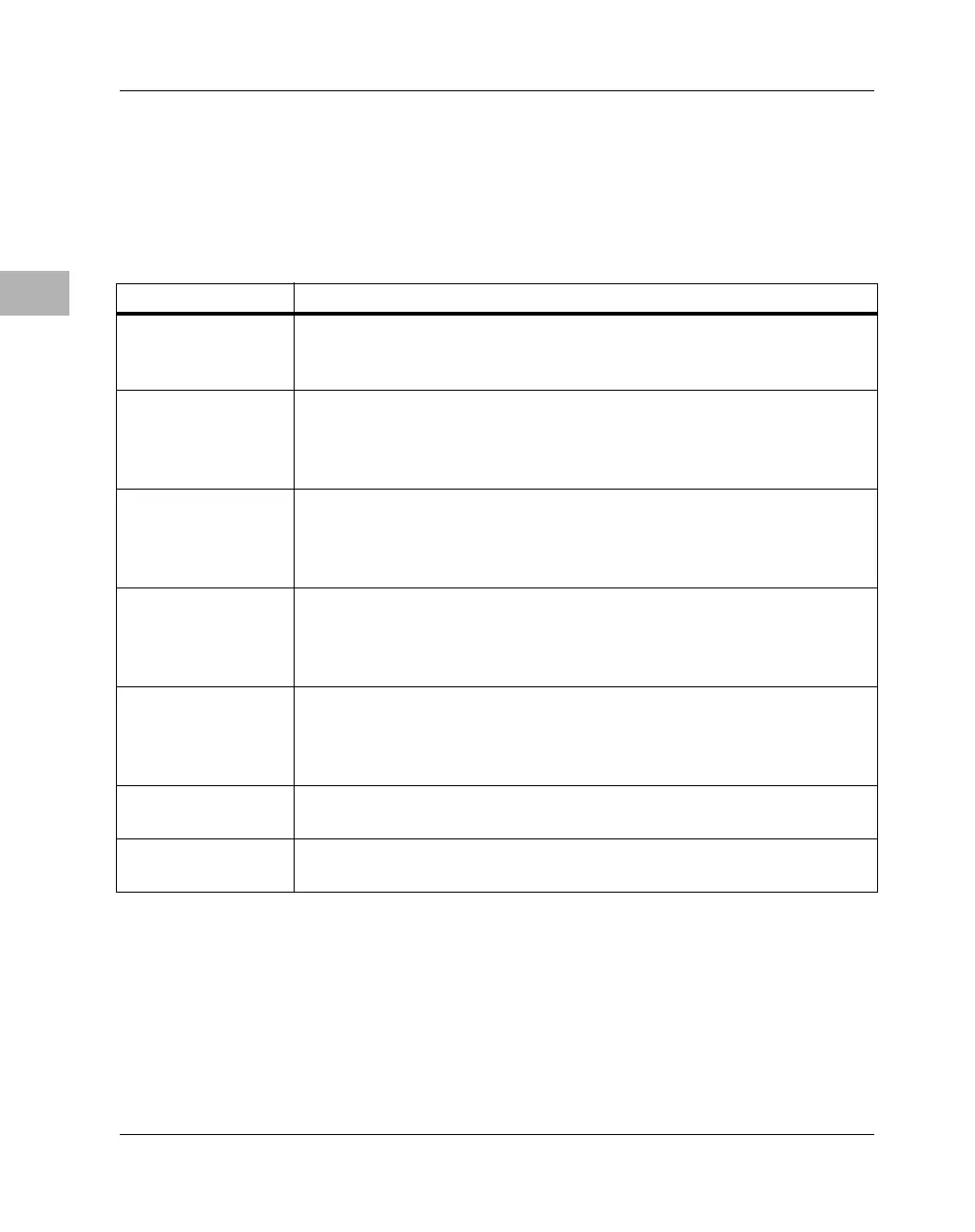

Table 4-6. Error Notification and Handling

Cause Action

Single-bit ECC Store: Write corrected data to memory

Load: Present corrected data to the MPC master

Generate interrupt via Raven MPIC if so enabled

Double-bit ECC Store: Terminate the bus cycle normally without writing to DRAM

Load: Present un-corrected data to the MPC master

Generate interrupt via Raven MPIC if so enabled

Generate Machine Check Interrupt to the Processor(s) if so enabled

MPC Bus Time Out Store: Discard write data and terminate bus cycle normally

Load: Present undefined data to the MPC master

Generate interrupt via Raven MPIC if so enabled

Generate Machine Check Interrupt to the Processor(s) if so enabled

PCI Target Abort Store: Discard write data and terminate bus cycle normally

Load: Return all 1’s and terminate bus cycle normally

Generate interrupt via Raven MPIC if so enabled

Generate Machine Check Interrupt to the Processor(s) if so enabled

PCI Master Abort Store: Discard write data and terminate bus cycle normally

Load: Return all 1’s and terminate bus cycle normally

Generate interrupt via Raven MPIC if so enabled

Generate Machine Check Interrupt to the Processor(s) if so enabled

PERR# Detected Generate interrupt via Raven MPIC if so enabled

Generate Machine Check Interrupt to the Processor(s) if so enabled

SERR# Detected Generate interrupt via Raven MPIC if so enabled

Generate Machine Check Interrupt to the Processor(s) if so enabled

Loading...

Loading...