3-36 Computer Group Literature Center Web Site

Falcon ECC Memory Controller Chip Set

3

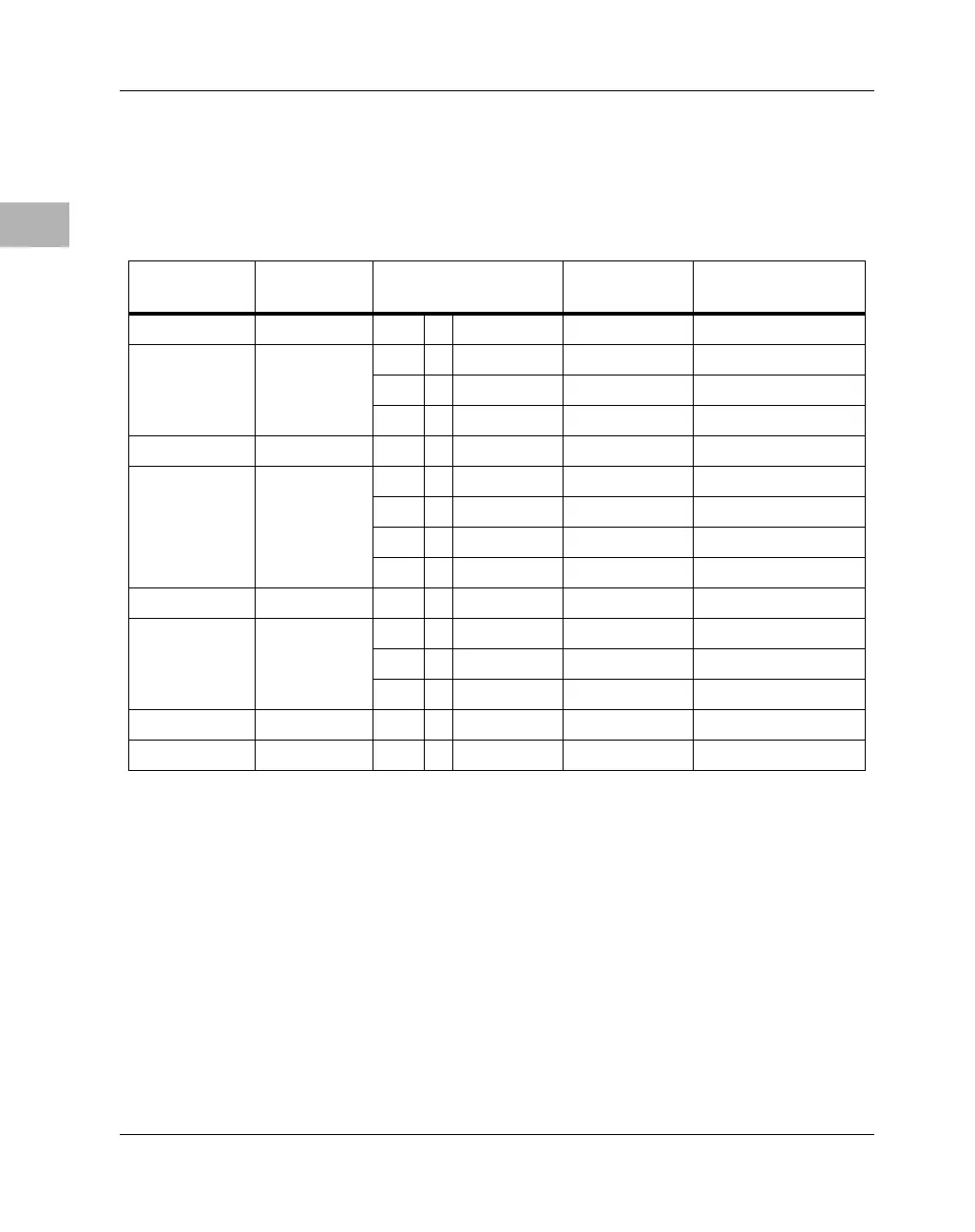

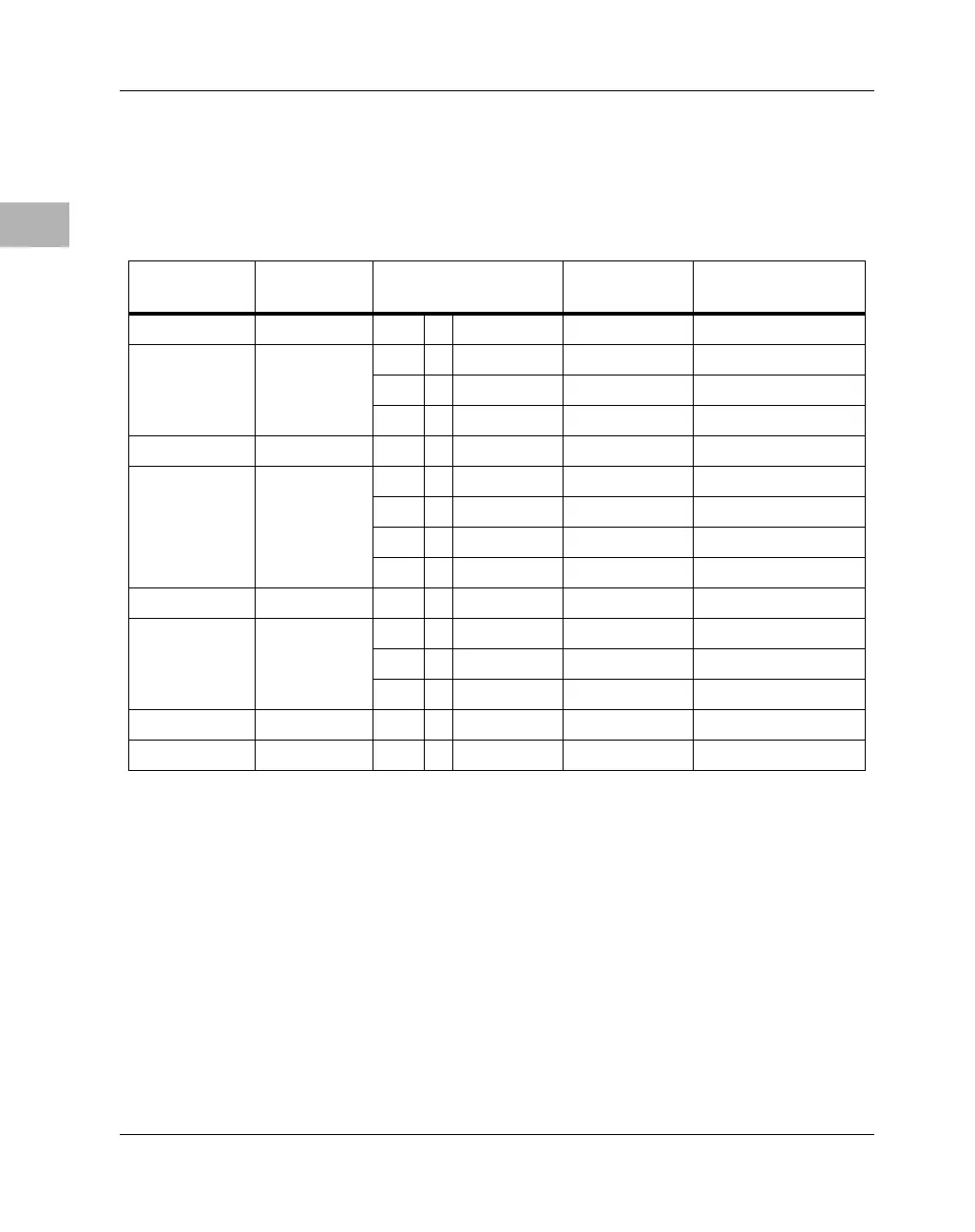

ram a/b/c/d siz0-2 These control bits define the size of their

corresponding block of DRAM. Table 3-13 shows the block configuration

assumed by the Falcon pair for each value of ram siz0-ram siz2.

Note It is important that all of the ram a/b/c/d siz0-2 bits be set to

accurately match the actual size of their corresponding blocks.

This includes clearing them to %000 if their corresponding

blocks are not present. Failure to do so will cause problems with

addressing and with scrub error logging.

Table 3-13. Block_A/B/C/D Configurations

ram a/b/c/d

siz0-2

Block

SIZE

Devices Used Technology Comments

%000 0MB - - - - Block Not Present

%001 16MB 36 - 1Mx4’s 4Mb

8 - 1Mx18’s 16Mb

4 - 1Mx36’s 4Mb/1Mb SIMM/DIMM

%010 32MB

18 - 2Mx8’s 16Mb

%011 64MB

144 - 4Mx1’s 4Mb

36 - 4Mx4’s 16Mb

8 - 4Mx18’s 64Mb

4 - 4Mx36’s 16Mb/4Mb SIMM/DIMM

%100 128MB

18 - 8Mx8’s 64Mb

%101 256MB

144 - 16Mx1’s 16Mb

36 - 16Mx4’s 64Mb

4 - 16Mx36’s 64Mb/16Mb SIMM/DIMM

%110 1024MB

144 - 64Mx1’s 64Mb

%111 0MB

--- - Reserved

Loading...

Loading...