ISA Local Resource Bus

http://www.motorola.com/computer/literature 1-23

1

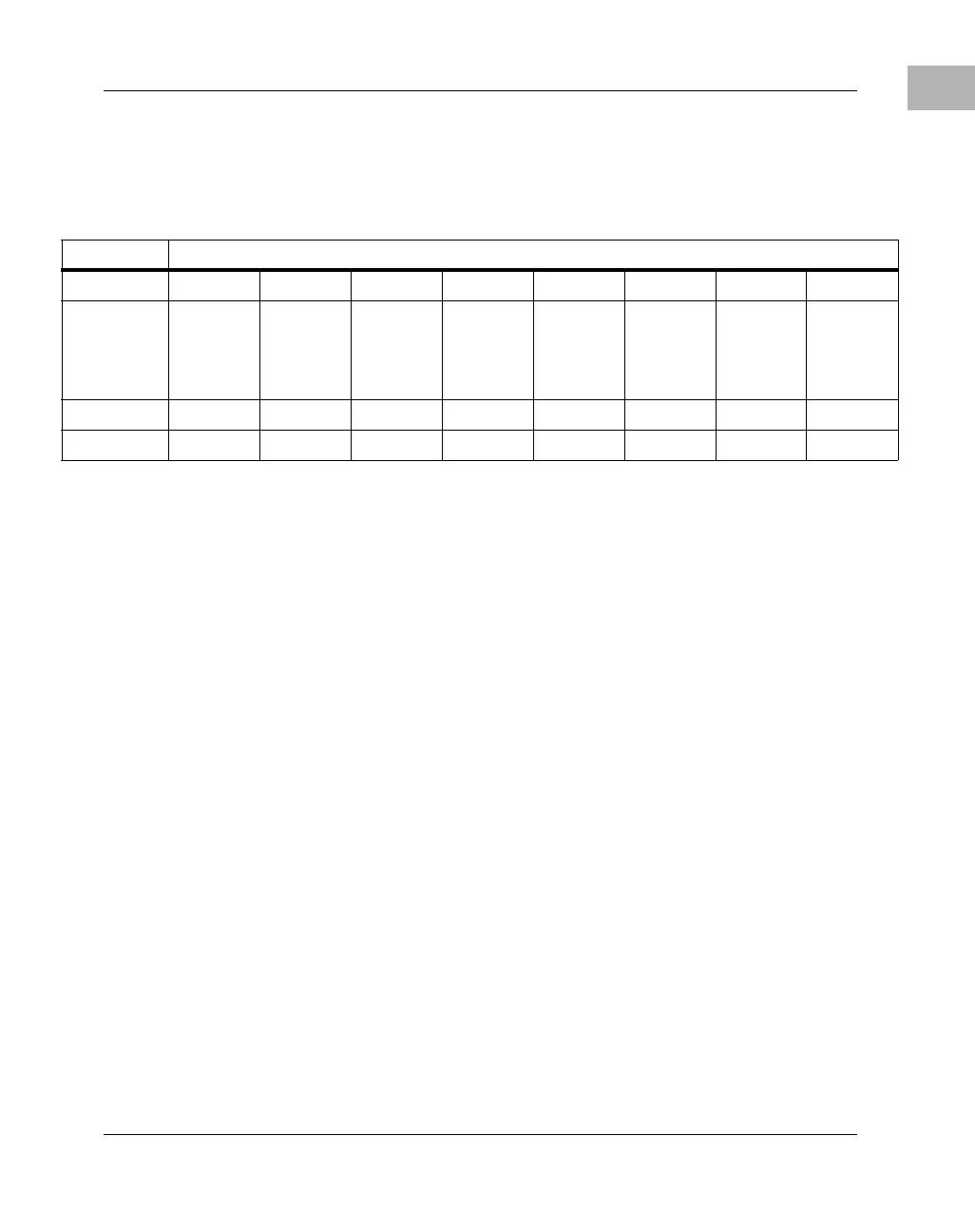

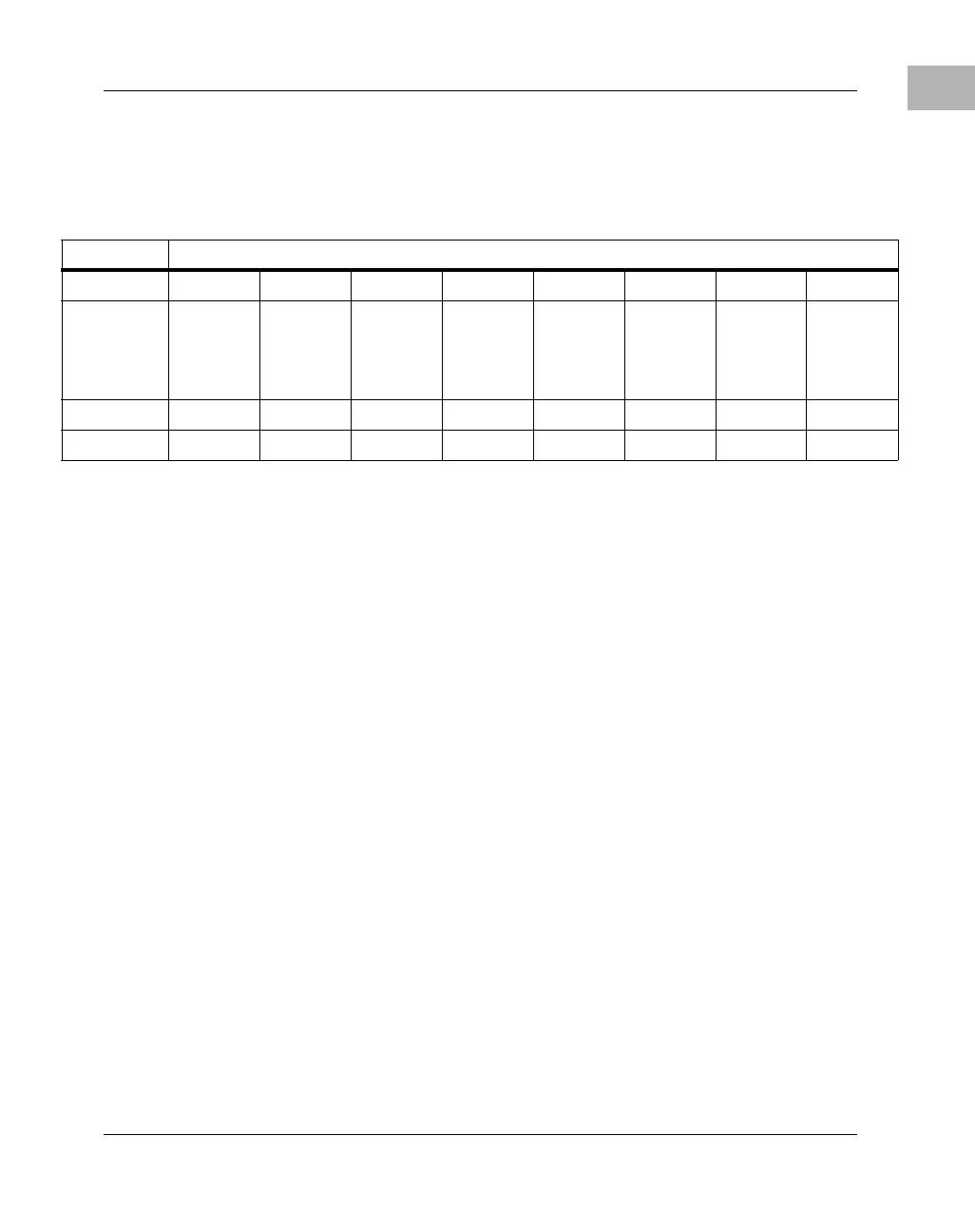

CPU Control Register

The CPU Control Register is accessed via the RD[32:39] data lines of the

upper Falcon device. This 8-bit register is defined as follows:

GETPCI Get PCI Bus. This bit is logically ORed with Raven’s PCI bus

request signal. It can be used to obtain the PCI bus for the Processor.

LEMODE Little-endian Mode. This bit must be set in conjunction with

the LEND bit in the Raven for little-endian mode.

P0/1_TBEN Processor 0/1 Time Base Enable. When this bit is cleared,

the TBEN pin of Processor 0/1 will be driven low.

ISA Local Resource Bus

W83C553 PIB Registers

The PIB contains ISA Bridge I/O registers for various functions. These

registers are accessible from the PCI bus. Refer to the W83C553 Data

Book for details.

Primary and Secondary EIDE Ports

The PIB also contains the EIDE controller. Refer to the 83C553 Data Book

for details.

Register CPU Control Register - $FEF88300

Bit 01234567

Field

GETPCI

LEMODE

P1_TBEN

P0_TBEN

Operation RRR/WR/WRRRR

Reset 0011XXXX

Loading...

Loading...