Programming Model

http://www.motorola.com/computer/literature 3-45

3

Note These test modes are not intended to be used once the chip is in a

system.

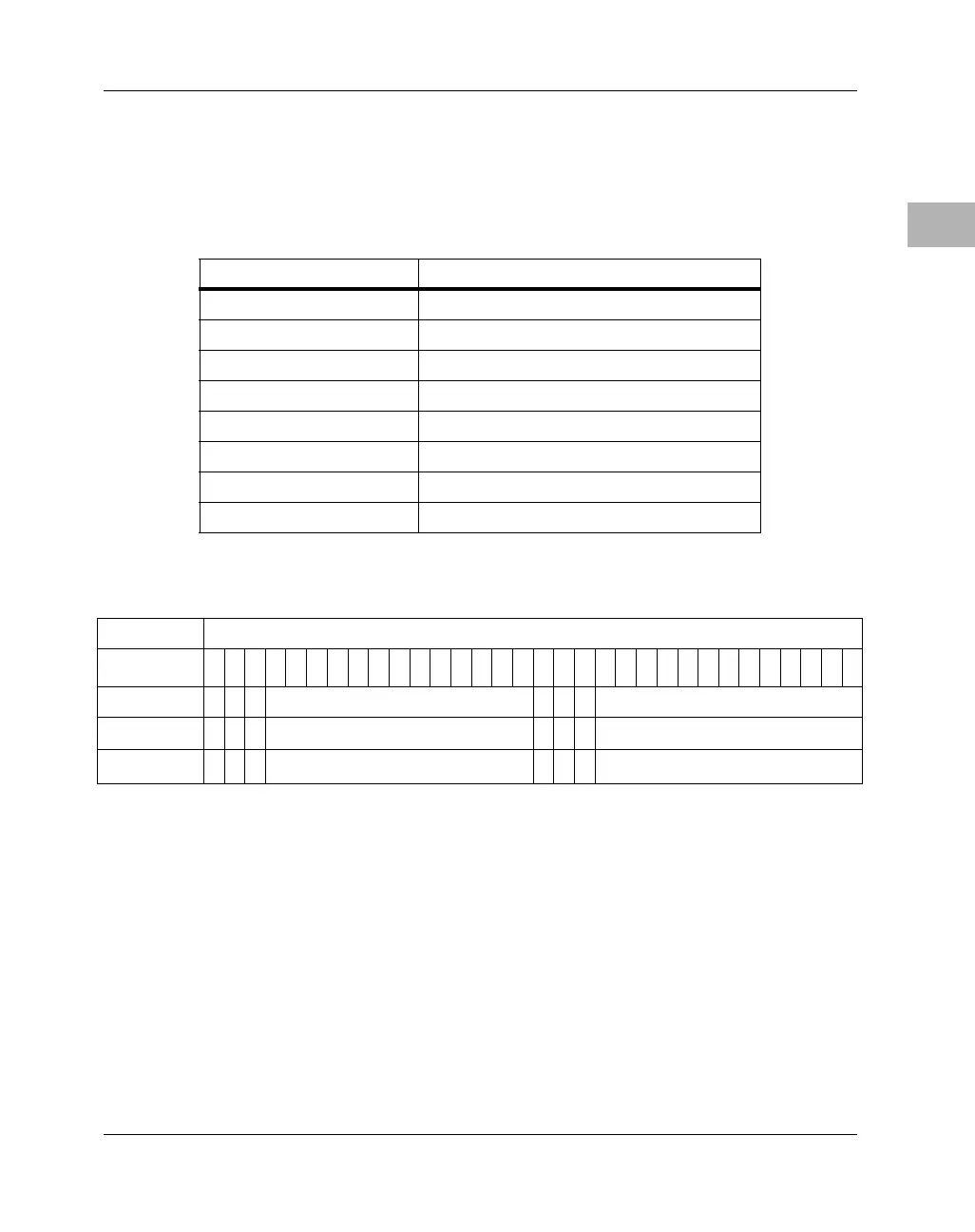

Refresh/Scrub Address Register

ROW ADDRESS These bits form the row address counter used by the

refresher/scrubber for all blocks of DRAM. The row address counter

increments by one after each refresh/scrub cycle. When it reaches all 1s, it

rolls back over to all 0s and continues counting. ROW ADDRESS is

readable and writable for test purposes.

Note Within each block, the most significant bits of ROW ADDRESS

are used only when their DRAM devices are large enough to

require them.

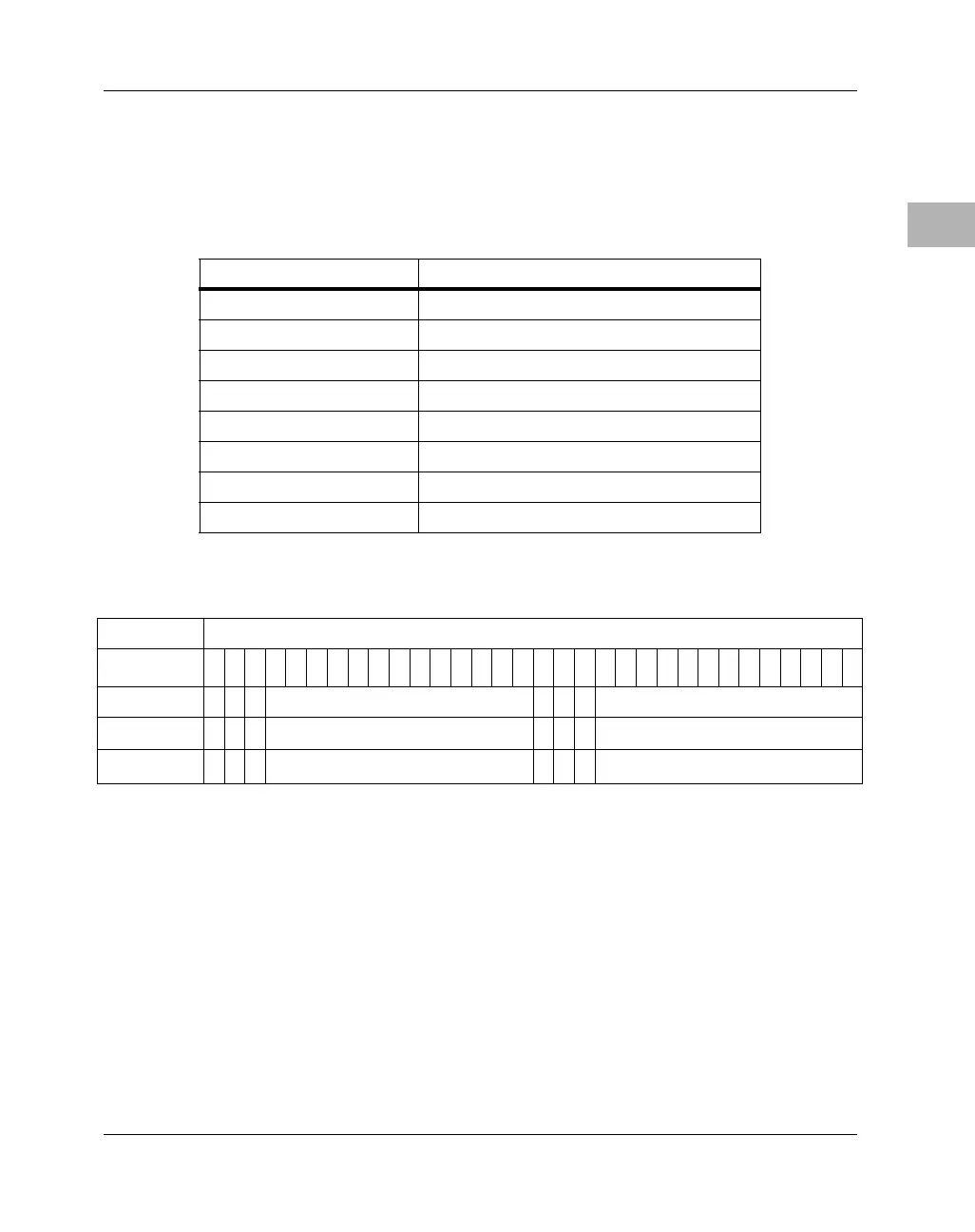

Table 3-14. rtest encodings

rtest0,rtest1,rtest2 Test Mode selected

%000 Normal Counter Operation

%001 RA counts at 16x

%010 RA counts at 256x

%011 RA is always at roll value for CA

%100 CA counts at 16x

%101 CA counts at 256x

%110 reserved

%111 reserved

Address

$FEF80048

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

0

0

0

ROW ADDRESS

0

0

0

COL ADDRESS

Operation

R

R

R

READ/WRITE

R

R

R

READ/WRITE

Reset

X

X

X

0 P

X

X

X

0 P

Loading...

Loading...