2-26 Computer Group Literature Center Web Site

Raven PCI Host Bridge & Multi-Processor Interrupt Controller

2

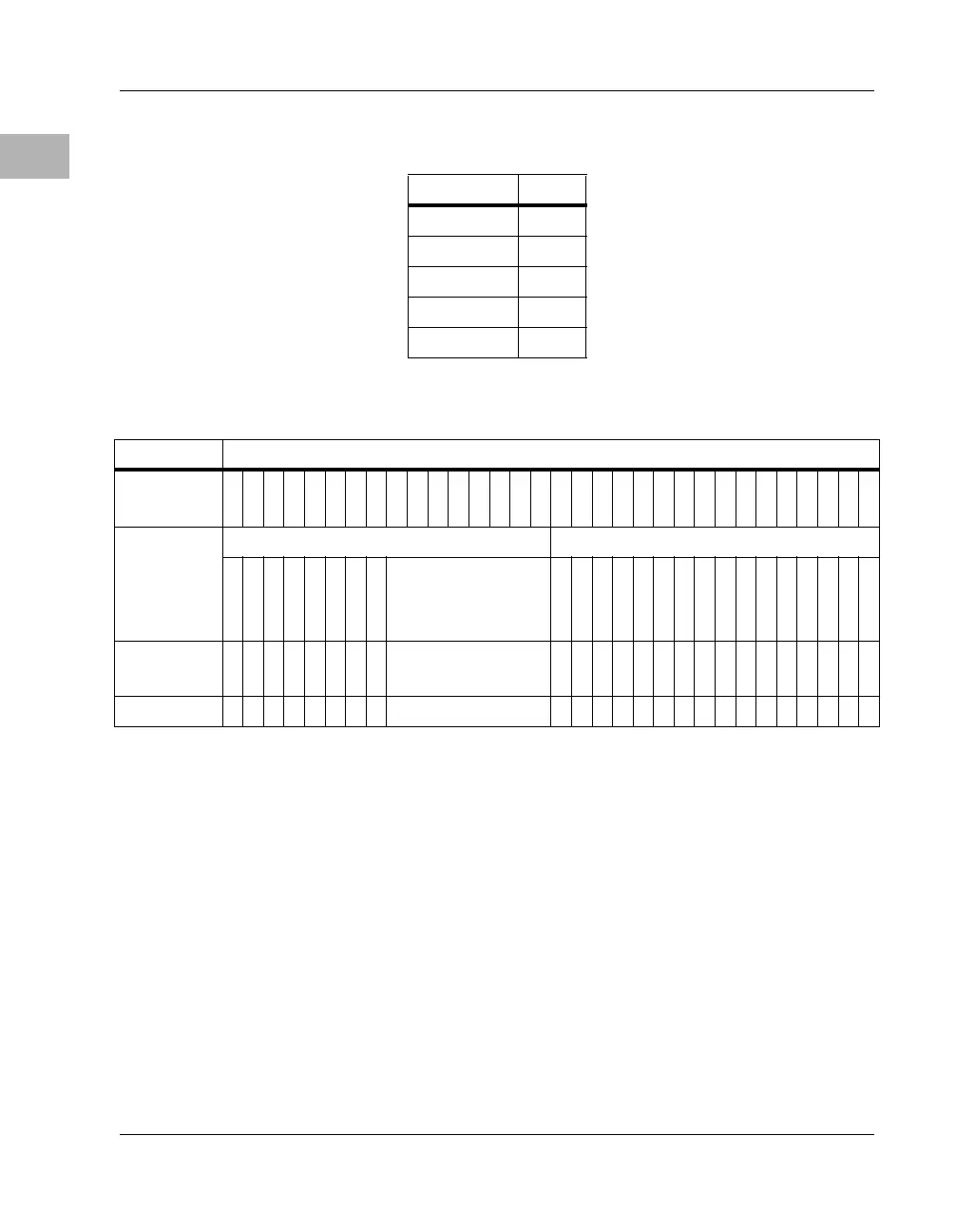

PPC Error Enable Register

DPEx Data Parity Error Enable. These bits are used for test reasons to

purposely inject data parity errors whenever Raven is sourcing PPC data.

A data parity error will be created on the corresponding PPC data parity

bus if a bit is set. For example, setting DPE0 will cause DP0 to be

generated incorrectly. If the bit is cleared, Raven will generate correct data

parity. These bits only have meaning if PPC data parity mode is enabled

DFLT Default PPC Master ID. This bit determines which MCHK* pin

will be asserted for error conditions in which the PPC master ID cannot be

determined or the Raven was the PPC master. For example, in event of a

PCI parity error for a transaction in which the Raven’s PCI master was not

involved, the PPC master ID cannot be determined. When DFLT is set,

MCHK1* is used. When DFLT is clear, MCHK0* will be used.

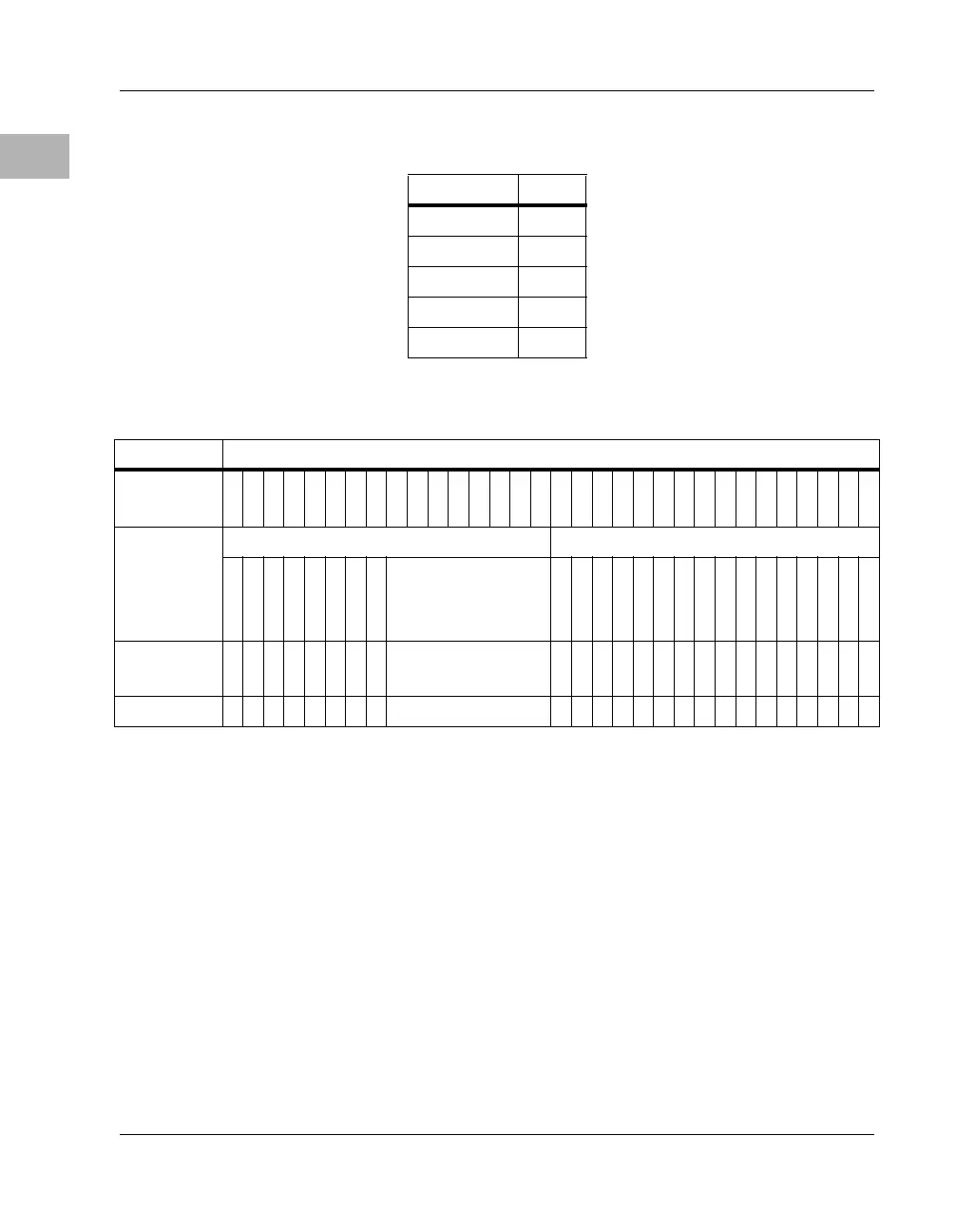

Frequency PADJ

66 $BE

50 $CE

40 $D8

33 $DF

25 $E7

Address $FEFF0020

Bit

0123456789

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

3

1

Name ERRTST ERREN

DPE0

DPE1

DPE2

DPE3

DPE4

DPE5

DPE6

DPE7

DFLT

PATOM

PDPEM

PERRM

SERRM

SMAM

RTAM

PATOII

PDPEI

PERRI

SERRI

SMAI

RTAI

Reset

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R/W

R/W

R/W

R/W

R/W

R/W

R/W

R

R

R/W

R/W

R/W

R/W

R/W

R/W

Address

0

0

0

0

0

0

0

0

$00

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Loading...

Loading...