3-44 Computer Group Literature Center Web Site

Falcon ECC Memory Controller Chip Set

3

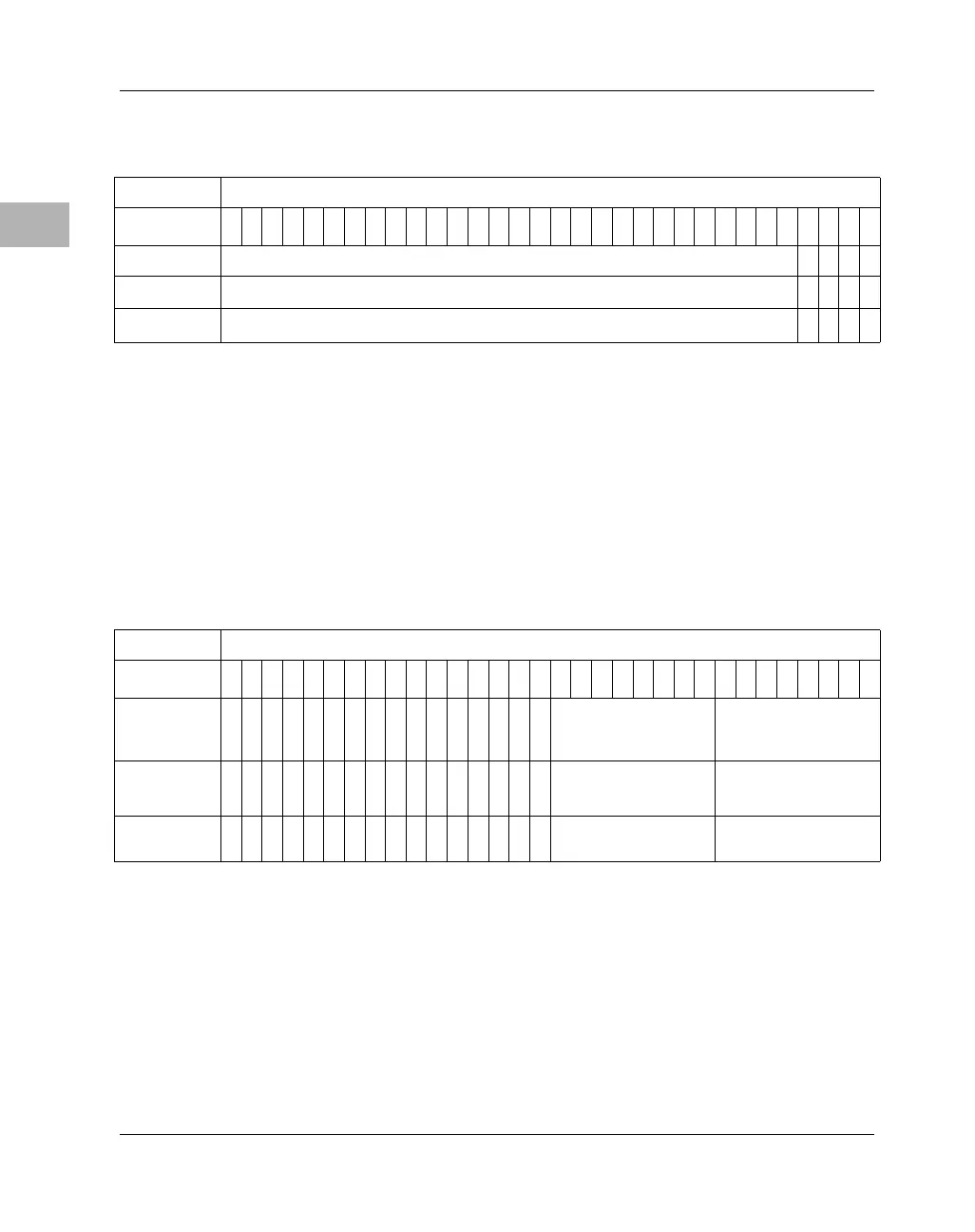

Error_Address Register

ERROR_ADDRESS These bits reflect the value that corresponds to bits

0-27 of the PowerPC 60x address bus when their Falcon last logged an

error during a PowerPC access to DRAM. They reflect the value of the

DRAM row and column addresses if the error was logged during a scrub

cycle. In this case, bits 2-14 correspond to row address signals 0-12

respectively and bits 15-27 correspond to column address signals 0-12

respectively. Refer to Table 3-20 on page 3-61. It shows how PowerPC

addresses correspond to DRAM row and column addresses.

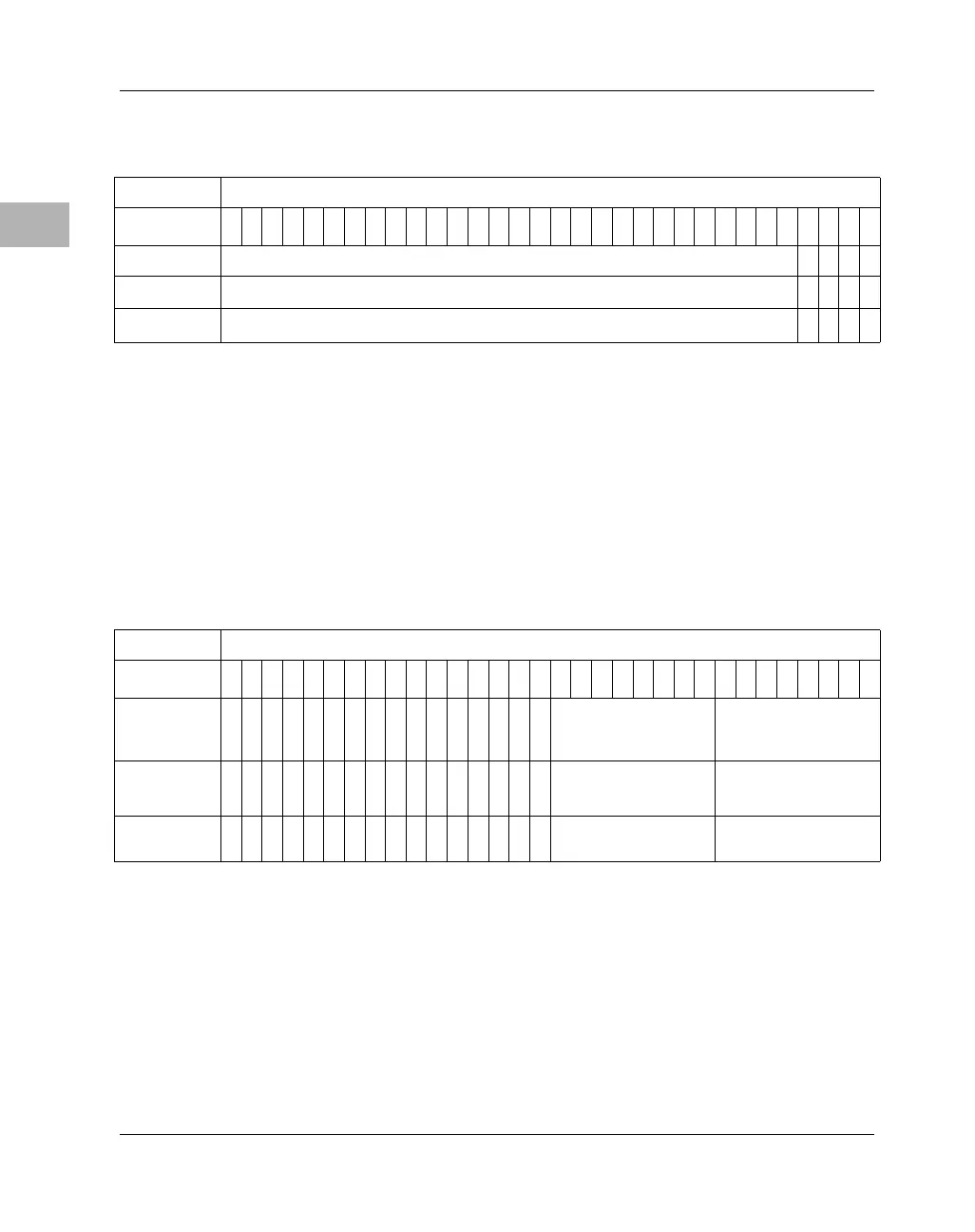

Scrub/Refresh Register

scb0,scb1 These bits increment every time the scrubber completes a scrub

of the entire DRAM. When these bits reach binary 11, they roll over to

binary 00 and continue. These bitsare cleared by power-up reset.

swen When set, swen allows the scrubber to perform write cycles. When

cleared, swen prevents scrubber writes.

rtest0,1,2 The rtest bits enable certain refresh counter test modes. Table

3-14 shows their encodings.

Address

$FEF80038

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

ERROR_ADDRESS

0

0

0

0

Operation

READ ONLY

R

R

R

R

Reset

X P

X

X

X

X

Address

$FEF80040

Bit

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

Name

scb0

scb1

0

0

0

0

0

swen

0

0

0

0

0

rtest0

rtest1

rtest2

Operation

R

R

R

R

R

R

R

R/W

R

R

R

R

R

R/W

R/W

R/W

READ ZERO READ ZERO

Reset

0 P

0 P

X

X

X

X

X

0 P

X

X

X

X

X

0 P

0 P

0 P

XX

Loading...

Loading...