2-32 Computer Group Literature Center Web Site

Raven PCI Host Bridge & Multi-Processor Interrupt Controller

2

WP Write Post Completion. This bit is set when the PCI master detects

an error while completing a write post transfer.

MIDx PPC Master ID. This field contains the ID of the PPC master

which originated the transfer in which the error occurred. The encoding

scheme is identical to that used in the GCSR register

COMMx PCI Command. This field contains the PCI command of the

PCI transfer in which the error occurred.

BYTEx PCI Byte Enable. This field contains the PCI byte enables of the

PCI transfer in which the error occurred. A set bit designates a selected

byte.

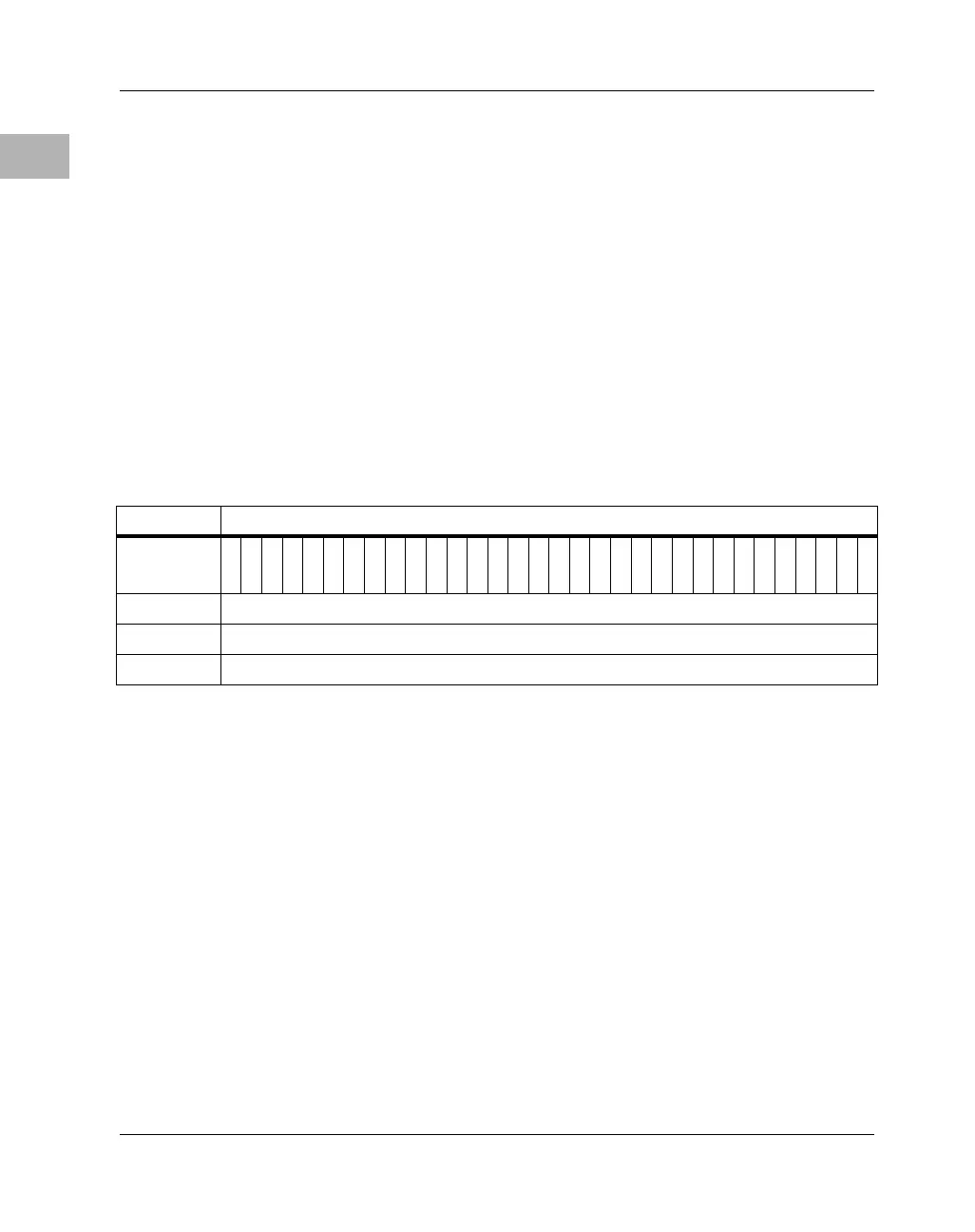

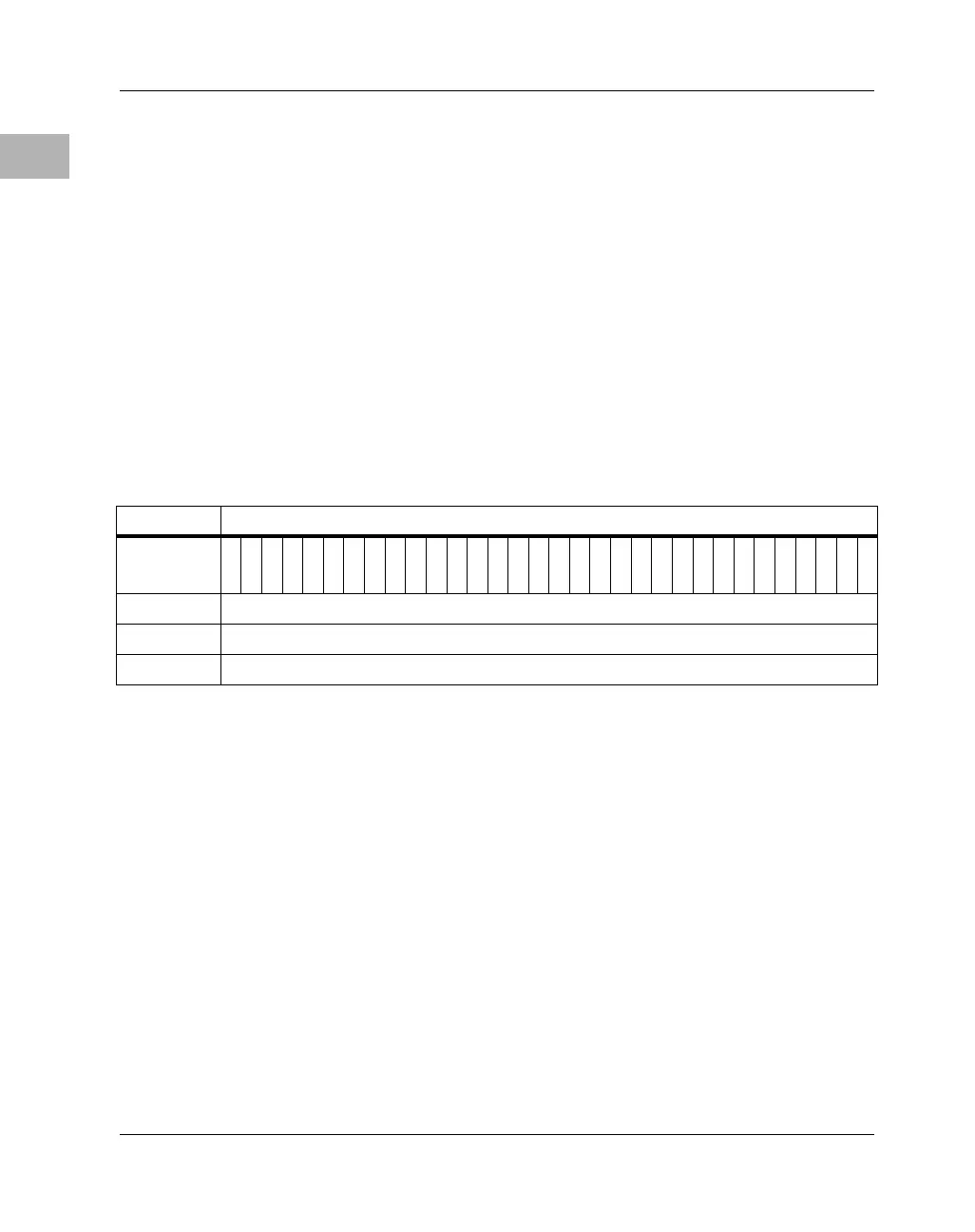

PCI Interrupt Acknowledge Register

PIACK PCI Interrupt Acknowledge. Performing a read from this

register will initiate a single PCI Interrupt Acknowledge cycle. Any single

byte or combination of bytes may be read from, and the actual byte enable

pattern used during the read will be passed on to the PCI bus. Upon

completion of the PCI interrupt acknowledge cycle, the Raven will present

the resulting vector information obtained from the PCI bus as read data.

Address $FEFF0030

Bit

0123456789

1

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

2

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

3

0

3

1

Name PIACK

Operation R

Reset $00000000

Loading...

Loading...