3-66 Computer Group Literature Center Web Site

Falcon ECC Memory Controller Chip Set

3

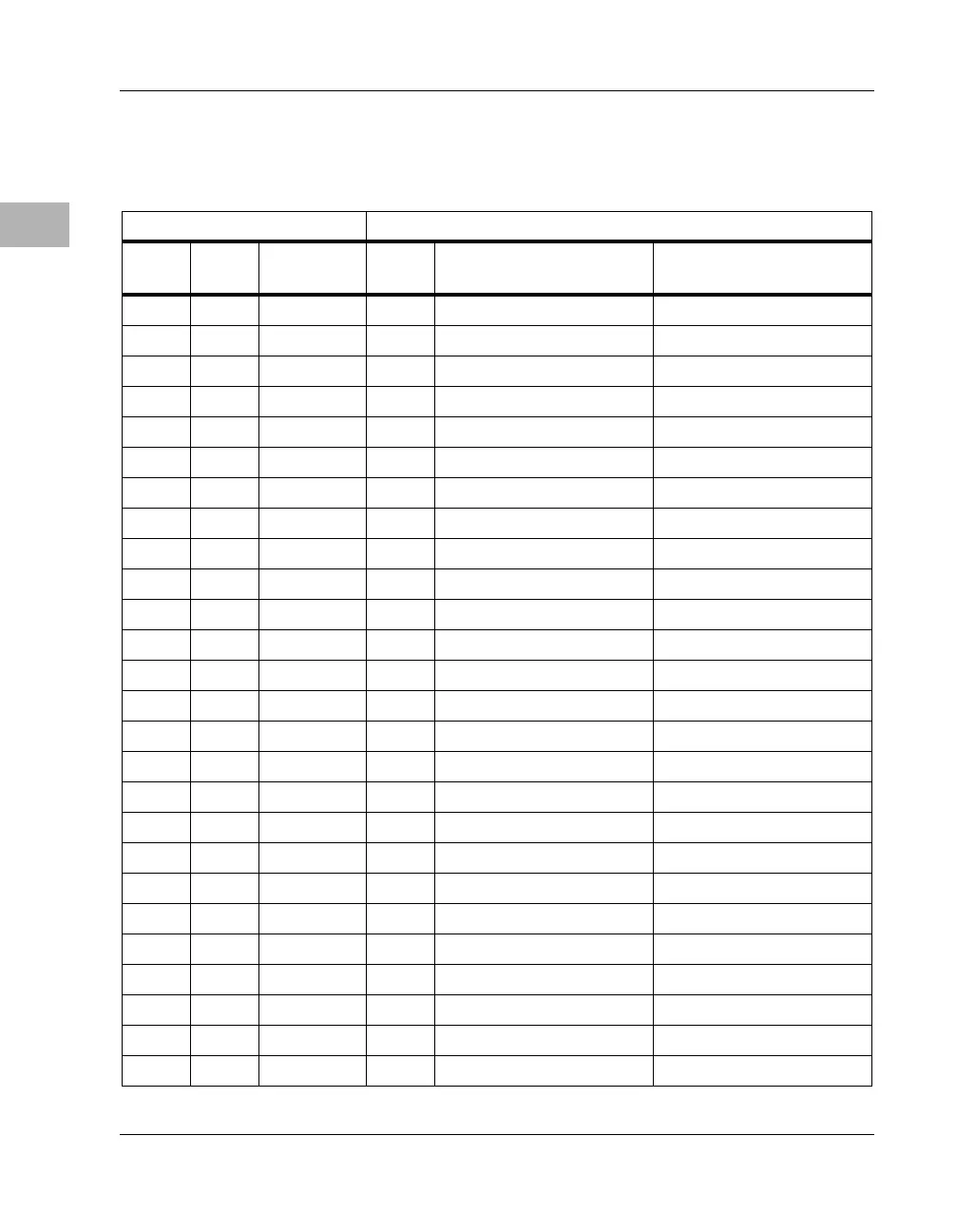

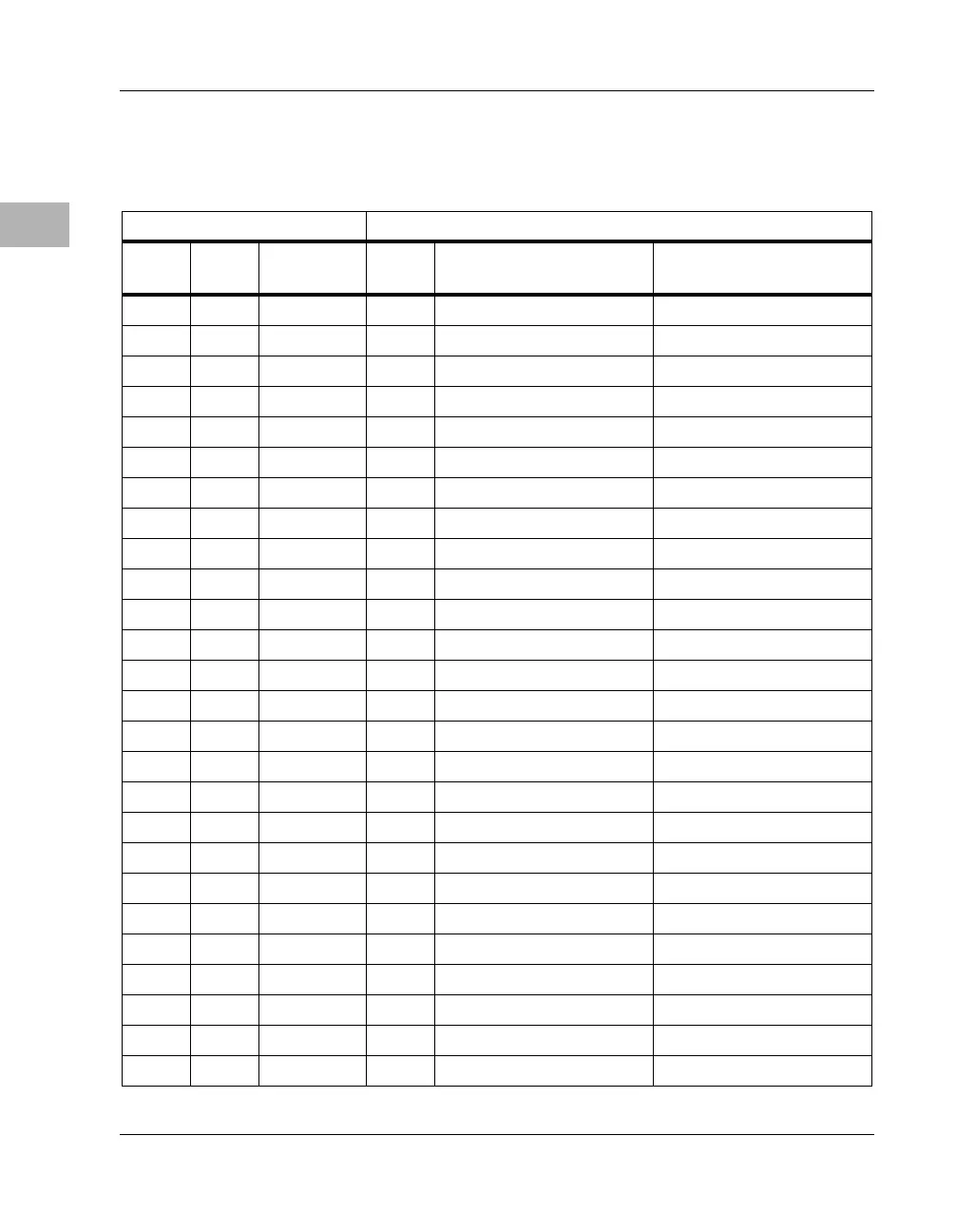

Table 3-23. PowerPC Data to DRAM Data Mapping

PowerPC DRAM Array

A[27] A[28] Data Bits RA[1

2]

Upper Falcon DRAM

Data Bits

Lower Falcon DRAM

Data Bits

0 0 dh[00:07] 0 rd[00:07] -

0 0 dh[08:15] 0 rd[08:15] -

0 0 dh[16:23] 0 rd[16:23] -

0 0 dh[24:31] 0 rd[24:31] -

0 0 dl[00:07] 0 - rd[00:07]

0 0 dl[08:15] 0 - rd[08:15]

0 0 dl[16:23] 0 - rd[16:23]

0 0 dl[24:31] 0 - rd[24:31]

0 1 dh[00:07] 0 rd[32:39] -

0 1 dh[08:15] 0 rd[40:47] -

0 1 dh[16:23] 0 rd[48:55] -

0 1 dh[24:31] 0 rd[56:63] -

0 1 dl[00:07] 0 - rd[32:39]

0 1 dl[08:15] 0 - rd[40:47]

0 1 dl[16:23] 0 - rd[48:55]

0 1 dl[24:31] 0 - rd[56:63]

1 0 dh[00:07] 1 rd[00:07] -

1 0 dh[08:15] 1 rd[08:15] -

1 0 dh[16:23] 1 rd[16:23] -

1 0 dh[24:31] 1 rd[24:31] -

1 0 dl[00:07] 1 - rd[00:07]

1 0 dl[08:15] 1 - rd[08:15]

1 0 dl[16:23] 1 - rd[16:23]

1 0 dl[24:31] 1 - rd[24:31]

1 1 dh[00:07] 1 rd[32:39] -

1 1 dh[08:15] 1 rd[40:47] -

Loading...

Loading...