Data Paths

http://www.motorola.com/computer/literature 3-67

3

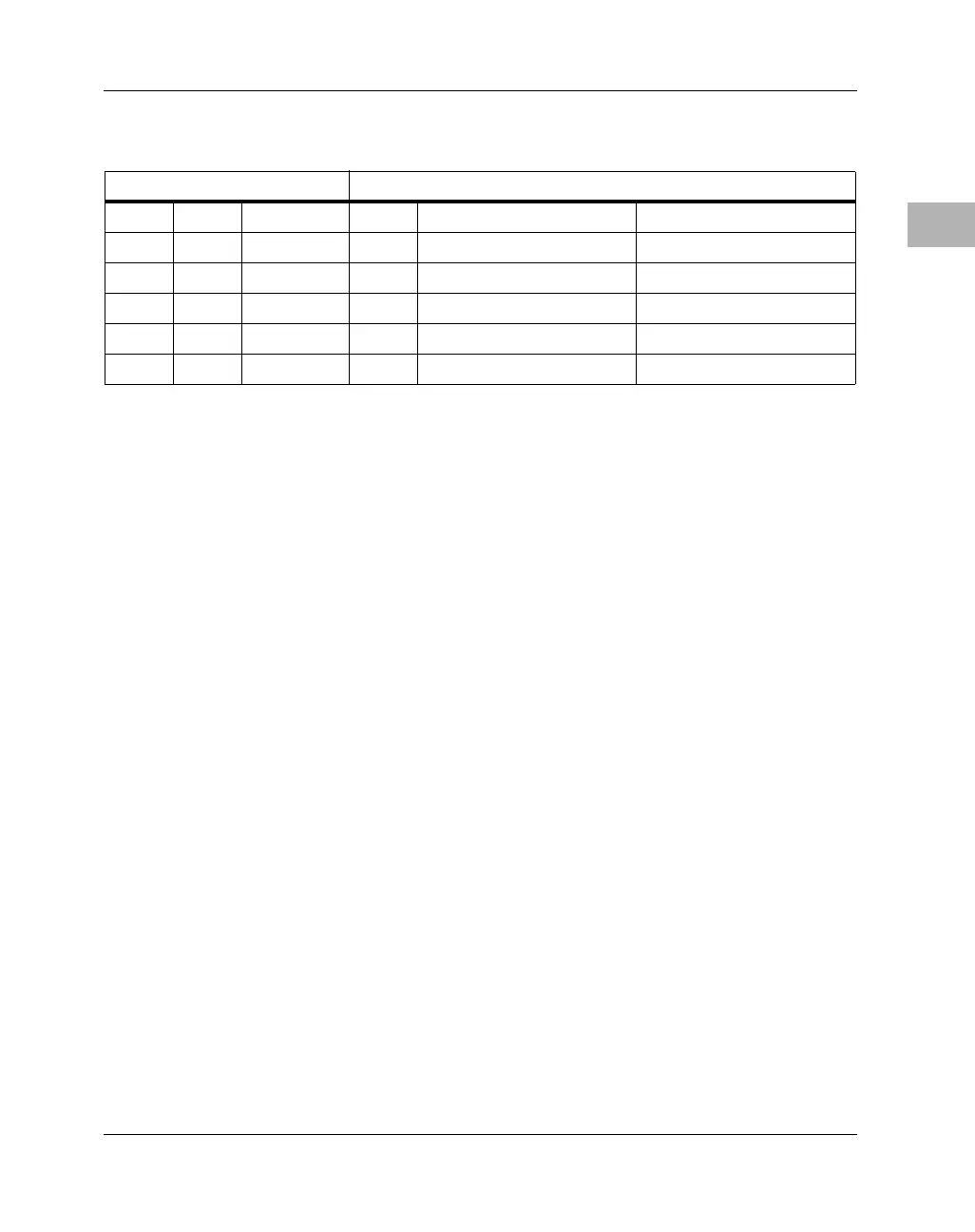

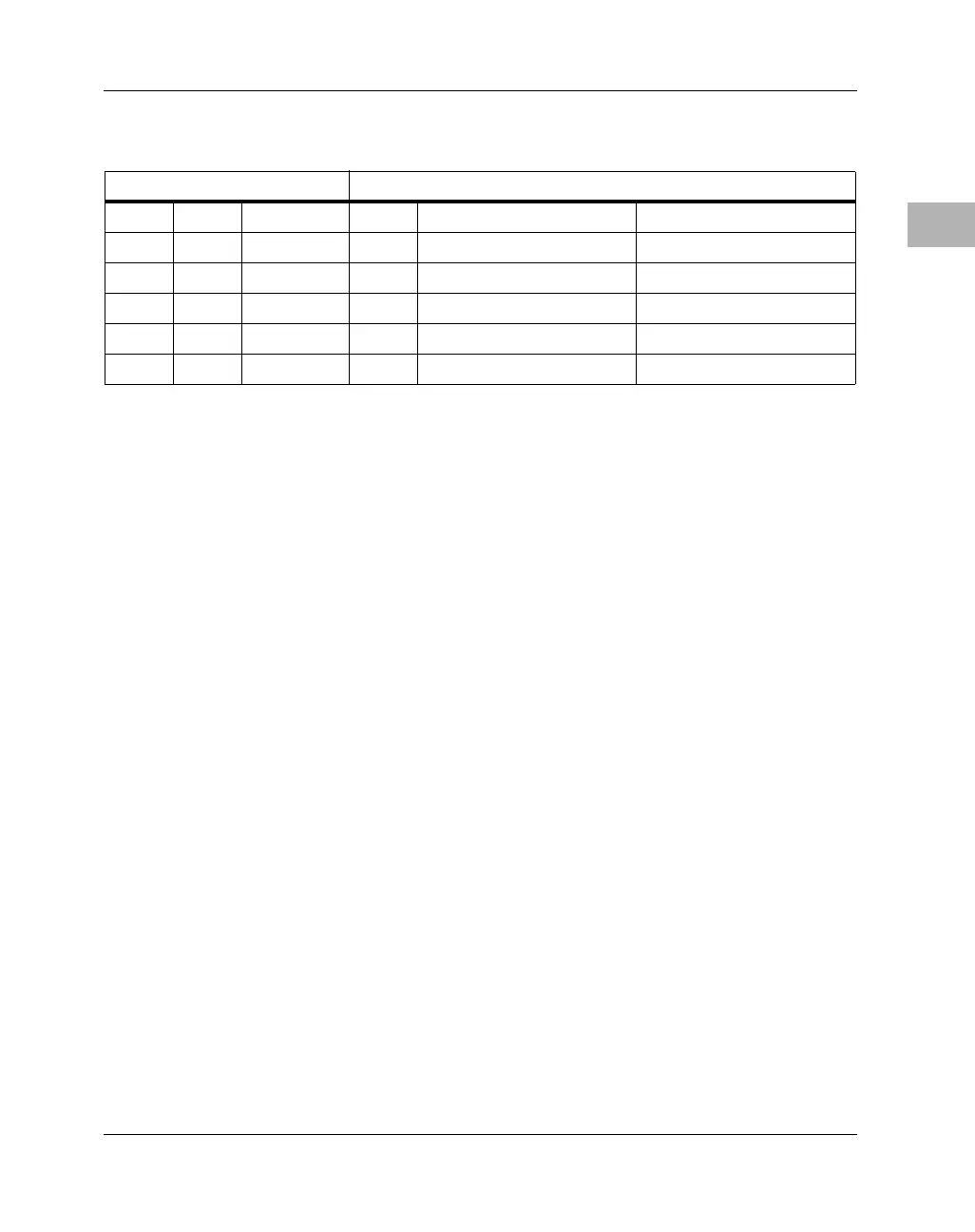

1 1 dh[16:23] 1 rd[48:55] -

1 1 dh[24:31] 1 rd[56:63] -

1 1 dl[00:07] 1 - rd[32:39]

1 1 dl[08:15] 1 - rd[40:47]

1 1 dl[16:23] 1 - rd[48:55]

1 1 dl[24:31] 1 - rd[56:63]

Table 3-23. PowerPC Data to DRAM Data Mapping (Continued)

PowerPC DRAM Array

Loading...

Loading...