2-24 Computer Group Literature Center Web Site

Raven PCI Host Bridge & Multi-Processor Interrupt Controller

2

PCIFBR PCI Flush Before Read. If set, the Raven will guarantee that

all PPC initiated read transactions will be completed before any PPC

initiated read transactions will be allowed to complete. When PCIFBR is

clear, there will be no correlation between these transaction types and their

order of completion. Please refer to the section on PCI/PPC Contention

Handling for more information.

BHOG Bus Hog. If set, the Raven PPC master will operate in the Bus Hog

mode. Bus Hog mode means the PPC master will continually request the

PPC bus for the entire duration of each PCI transfer. If Bus Hog is not

enabled, the PPC master will request the bus in a normal manner. Please

refer to the section on PPC Master for more information.

PPCFBR PPC Flush Before Read. If set, the Raven will guarantee that all

PCI initiated posted write transactions will be completed before any PPC

initiated read transactions will be allowed to complete. When PPCFBR is

clear, there will be no correlation between these transaction types and their

order of completion. Please refer to the section on PCI/PPC Contention

Handling for more information.

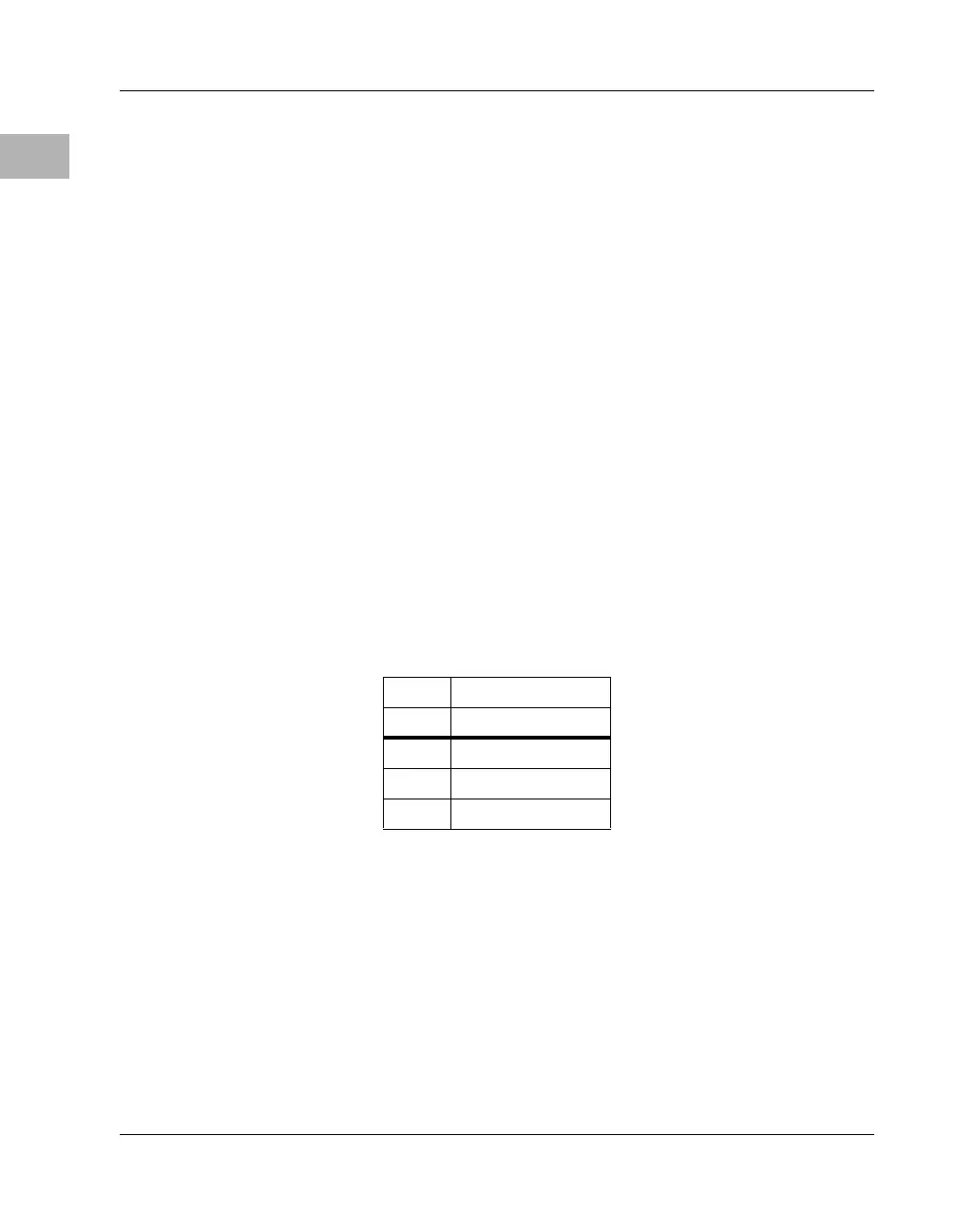

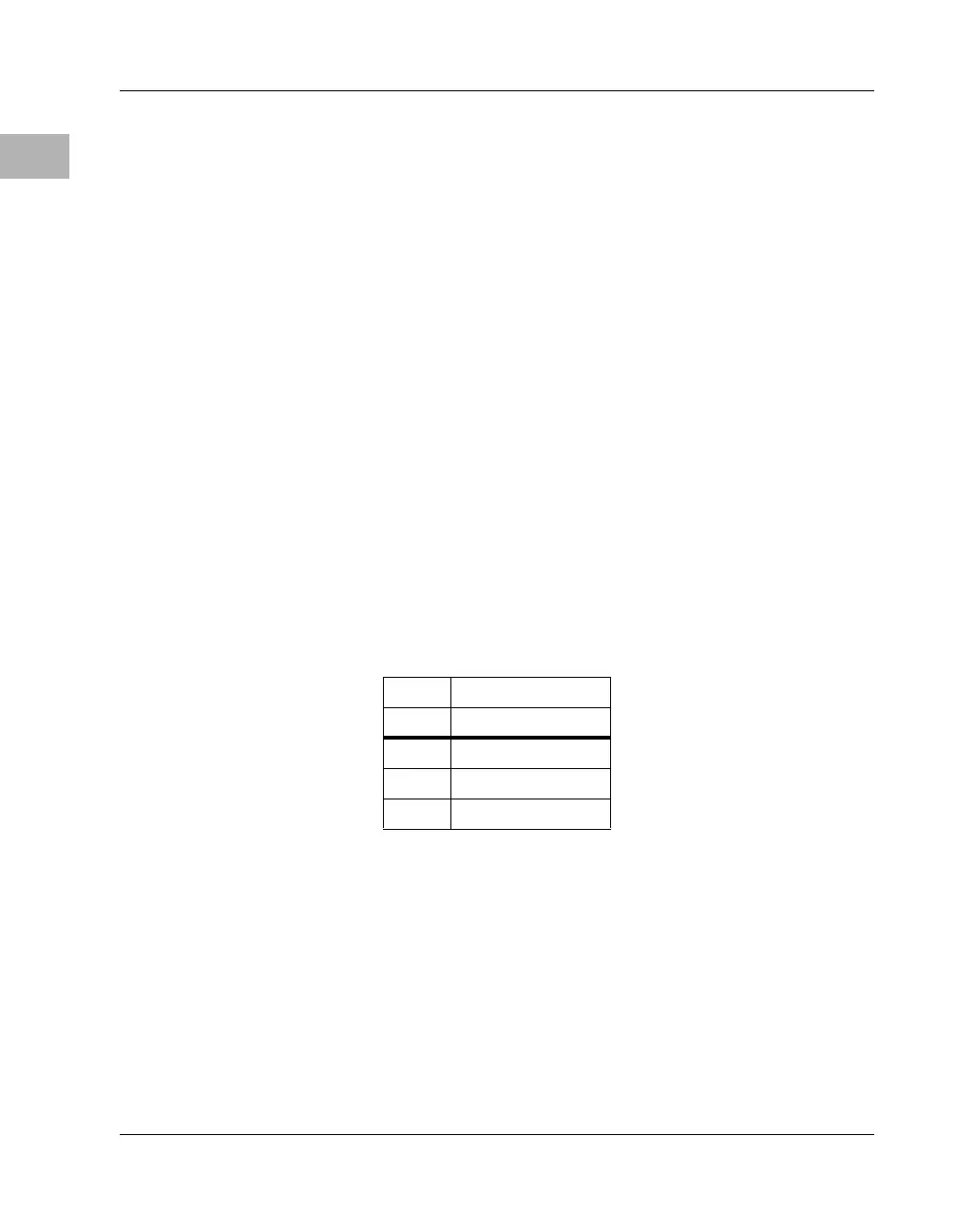

PBTx PPC Bus Time-out. This field specifies the PPC bus time-out

length. The time-out length is encoded as follows:

P64 64-bit PCI Mode Enable. If set, the Raven is connected to a 64-bit

PCI bus.

OPIC OpenPIC Interrupt Controller Enable. If set, the Raven internal

OpenPIC interrupt controller is enabled. If cleared, Raven detected errors

will be passed on to processor 0 INT pin.

MBT Time Out Length

00 256

µ

sec

01 64

µ

sec

10 8

µ

sec

11 disabled

Loading...

Loading...