Functional Description

http://www.motorola.com/computer/literature 3-9

3

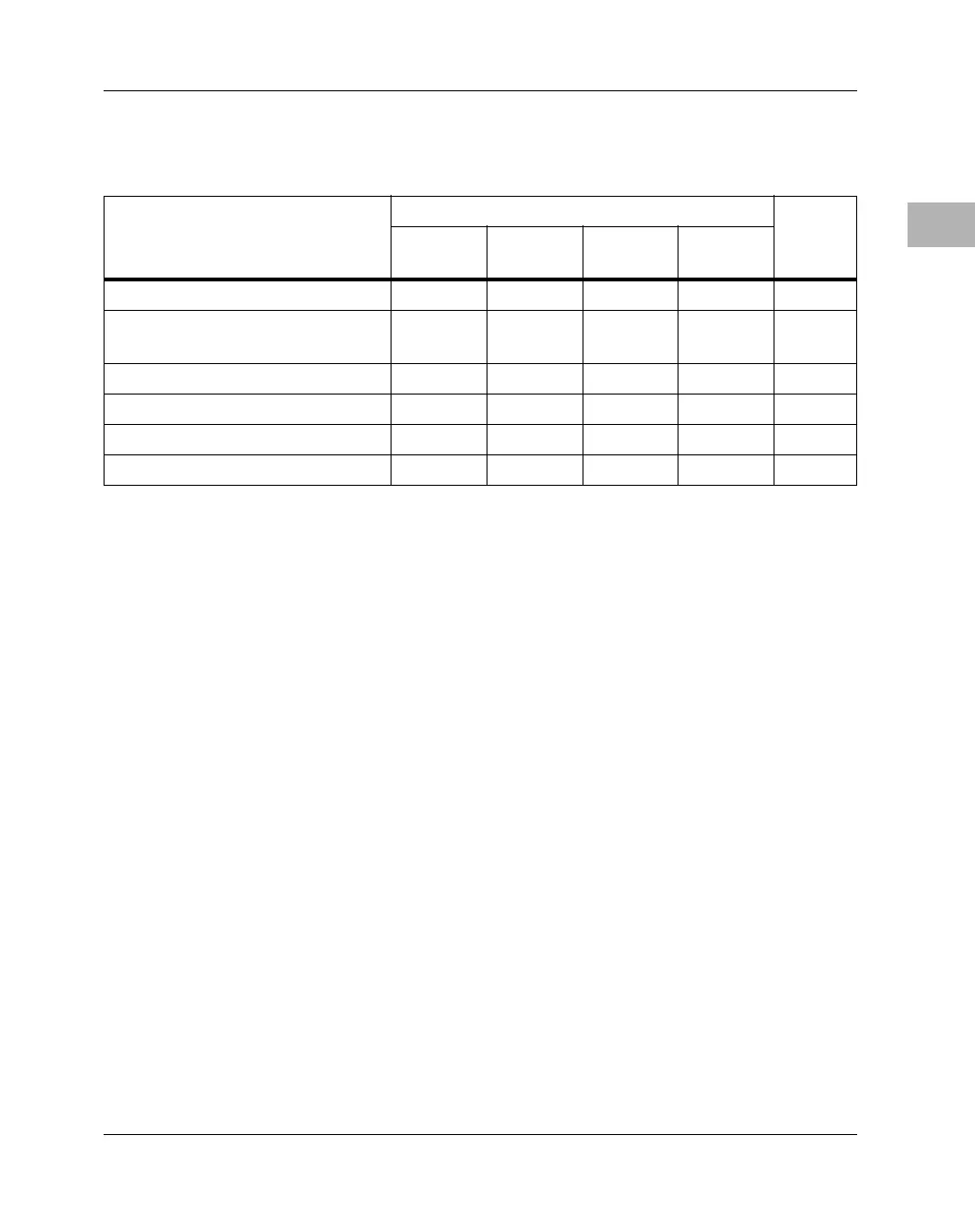

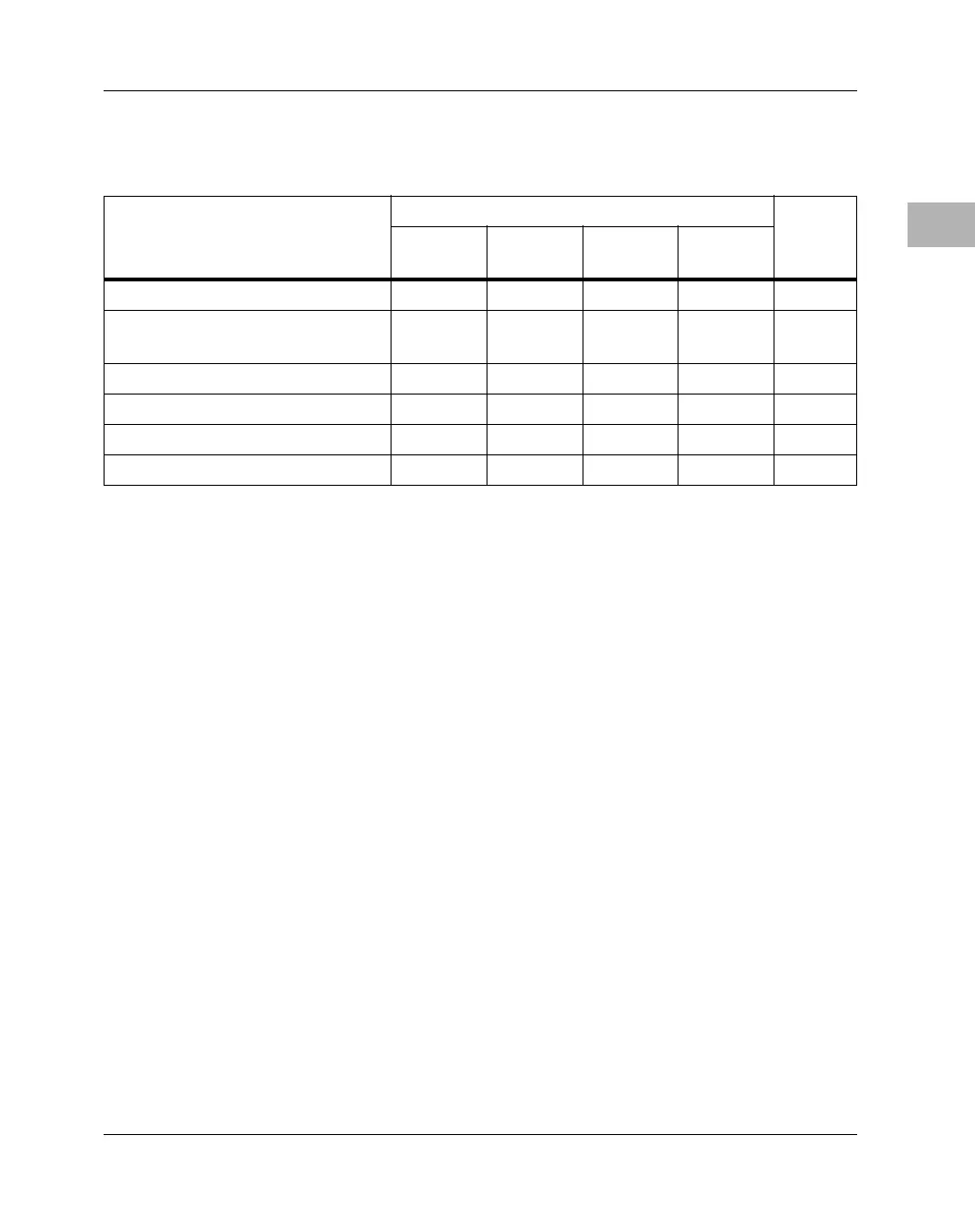

Notes

1. These numbers assume that the PowerPC 60x bus master is doing

address pipelining with TS_ occurring at the minimum time after

AACK_ is asserted. Also the two numbers shown in the 1st beat

column are for page miss/page hit.

4-Beat Write after Idle

4111

7

4-Beat Write after 4-Beat Write

(Quad-word aligned)

7/3

1

1 1 1 10/6

1-Beat Read after Idle

9---

9

1-Beat Read after 1-Beat Read

9/6

1

---

9/6

1-Beat Write after Idle

4

---4

1-Beat Write after 1-Beat Write

13/10

1

---13/10

Table 3-2. PowerPC 60x Bus to DRAM Access Timing when Configured for

60ns Fast Page Devices (Continued)

ACCESS TYPE

CLOCK PERIODS REQUIRED FOR:

Total

Clocks

1st

Beat

2nd

Beat

3rd

Beat

4th

Beat

Loading...

Loading...