Rev. 7.00 Mar 10, 2005 page xviii of xlii

Item Page Revision (See Manual for Details)

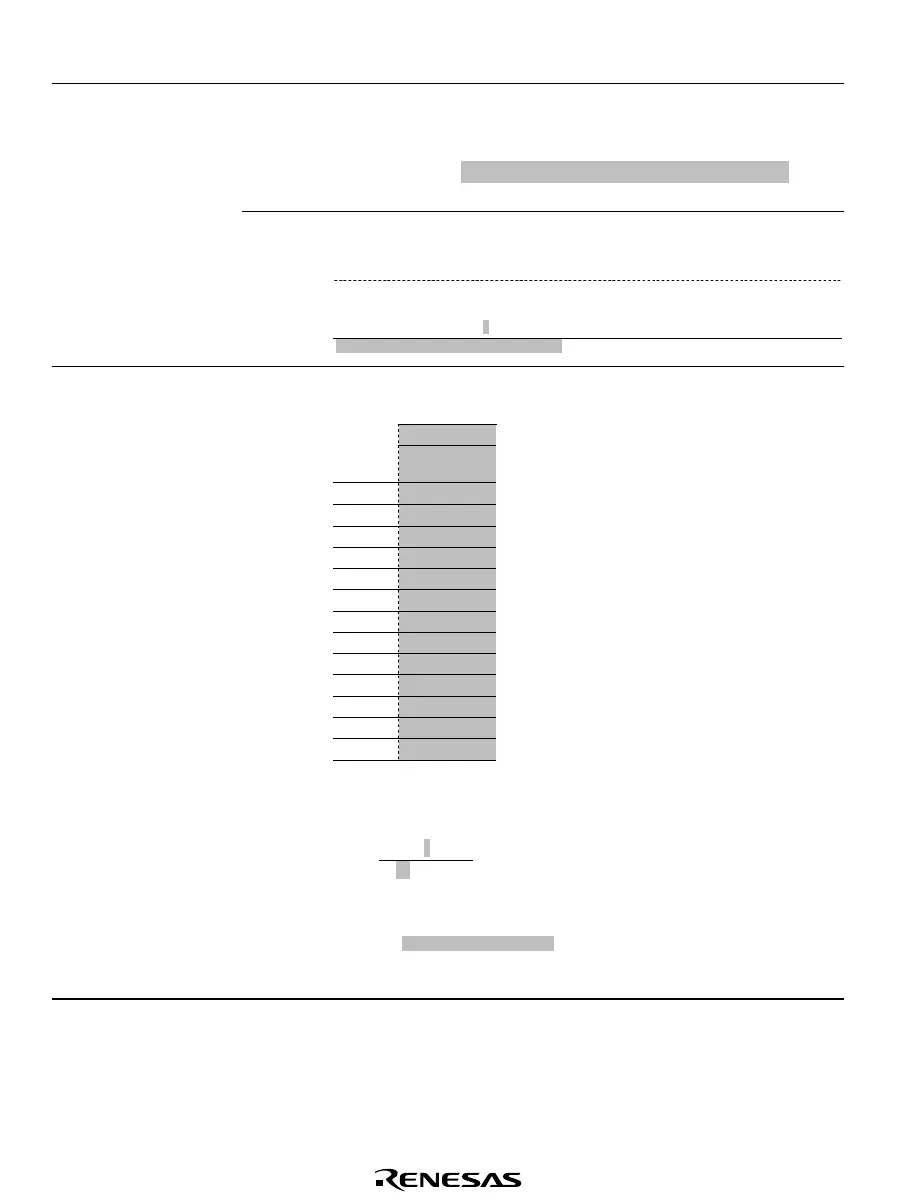

9.7.5 Application

Notes

328 Description amended

2. Use a clock with a frequency of up to 16 MHz for input to the

AEVH and AEVL pins, and ensure that the high and low widths

of the clock are

at least half the OSC clock cycle duration. The

duty cycle is immaterial.

329 Description amended

Mode

Maximum AEVH/AEVL Pin Input

Clock Frequency

Watch, subactive, subsleep, standby (φw/2)

(φw/4)

φw = 32.768 kHz or 38.4 kHz

*

(φw/8)

1000 kHz

500 kHz

250 kHz

Note: * Does not apply to H8/38124 Group.

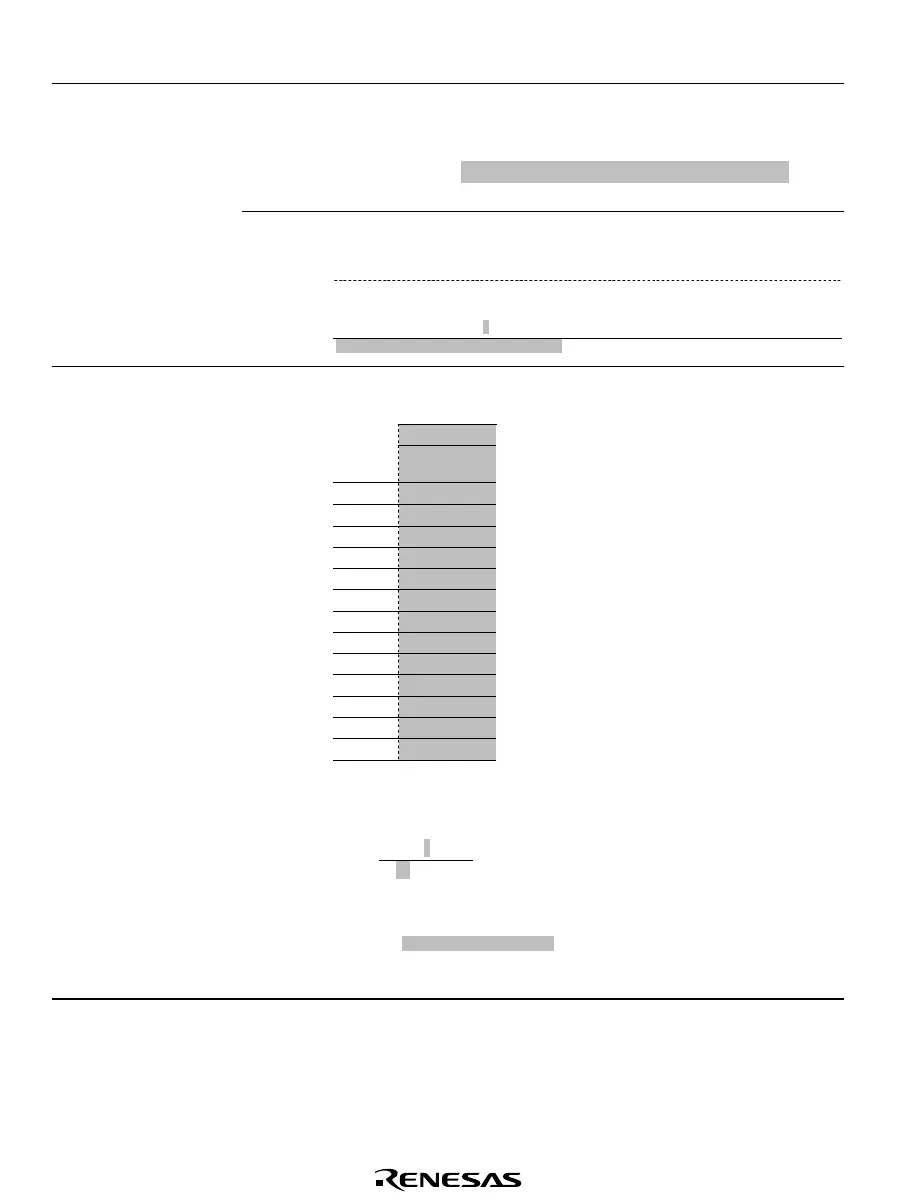

10.2.8 Bit Rate

Register (BRR)

Table 10.3 Examples

of BRR Settings for

Various Bit Rates

(Asynchronous

Mode) (2)

349 Table amended

φ

10 MHz

Bit Rate

(bit/s)

n N

Error

(%)

110 3 43 0.88

150 3 32 –1.36

200 3 23 1.73

250 3 19 –2.34

300 3 15 1.73

600 3 7 1.73

1200 3 3 1.73

2400 3 1 1.73

4800 3 0 1.73

9600 2 1 1.73

19200 2 0 1.73

31250 0 9 0

38400 0 7 1.73

Notes amended

1. The value set in BRR is given by the following equation:

φ

N =

(

32 • 2

2n

• B)

– 1

where B: Bit rate (bit/s)

N: Baud rate generator BRR setting (0 ≤ N ≤ 255)

φ: System clock frequency

n: Baud rate generator input clock number (n = 0, 2, or 3)

(The relation between n and the clock is shown in table 10.4.)

Loading...

Loading...