Saia-Burgess Controls AG

Manual I/O-modules for PCD1 │ PCD2 series │ Document 27-600 – Release ENG09 │ 2019-05-01

5-53

I/O modules PCD1|PCD2

PCD2.W10x

5

5.8.1 PCD2.W10x, analogue inputs, 4 channels, 12 bit resolution

High-speed module for general use for recording analogue signals with a conver-

siontimeof≤30µsandaresolutionof12bits.

Module overview

PCD2.W100 4channelsforsignals0 … 10V

Unipolar*): 0V … +10Vor–10V … 0V

Bipolar*): –10V … +10V

Inputresistance:>10MΩ

PCD2.W105 4channelsforsignals0 … 20mA

Unipolar*): 0 … +20mAor-20 … 0mA

Bipolar*): -20mA … +20mA

Circuitresistance(Rshunt):100Ω/0.1%

*)Unipolar-bipolar,switchablewithjumper

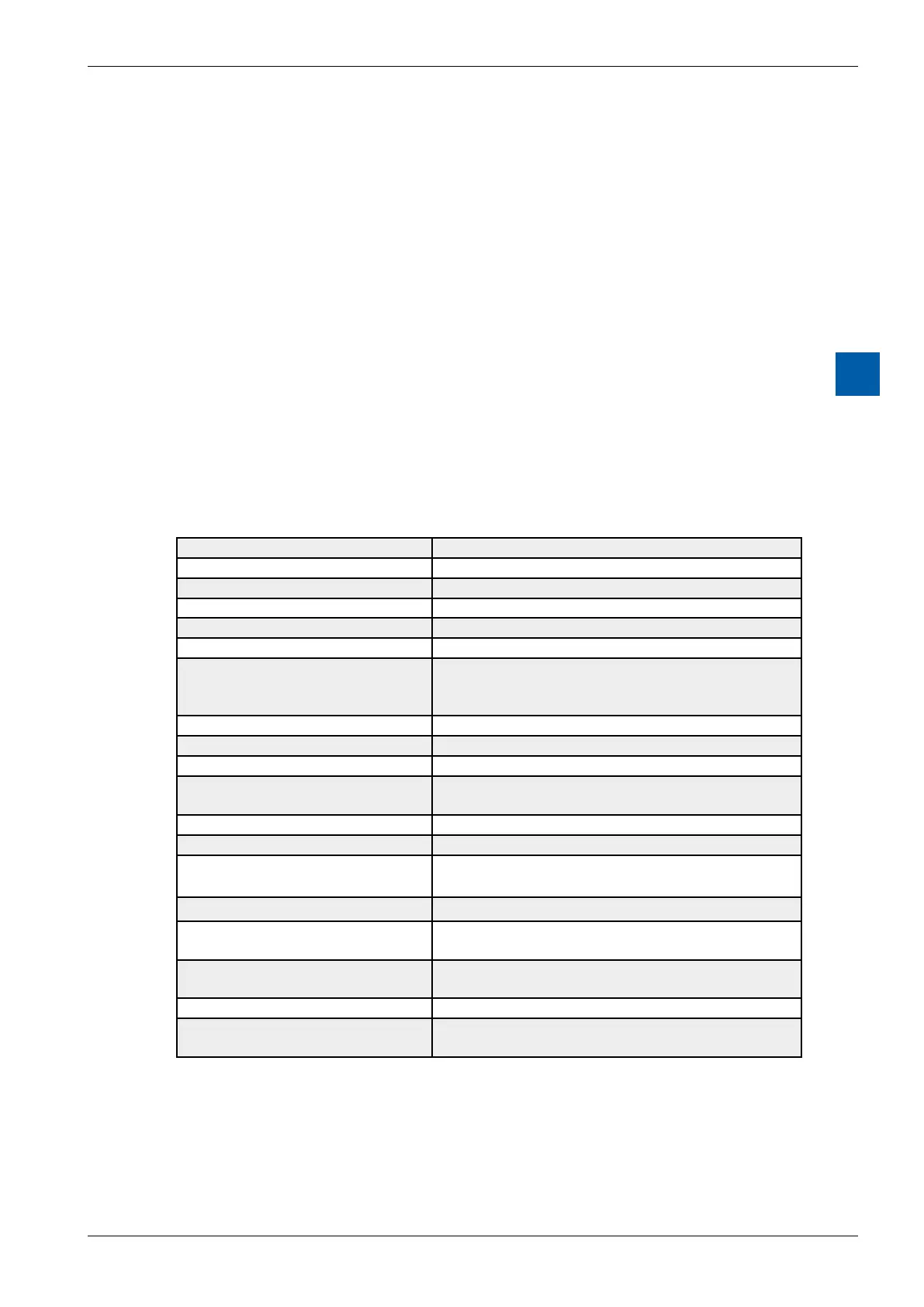

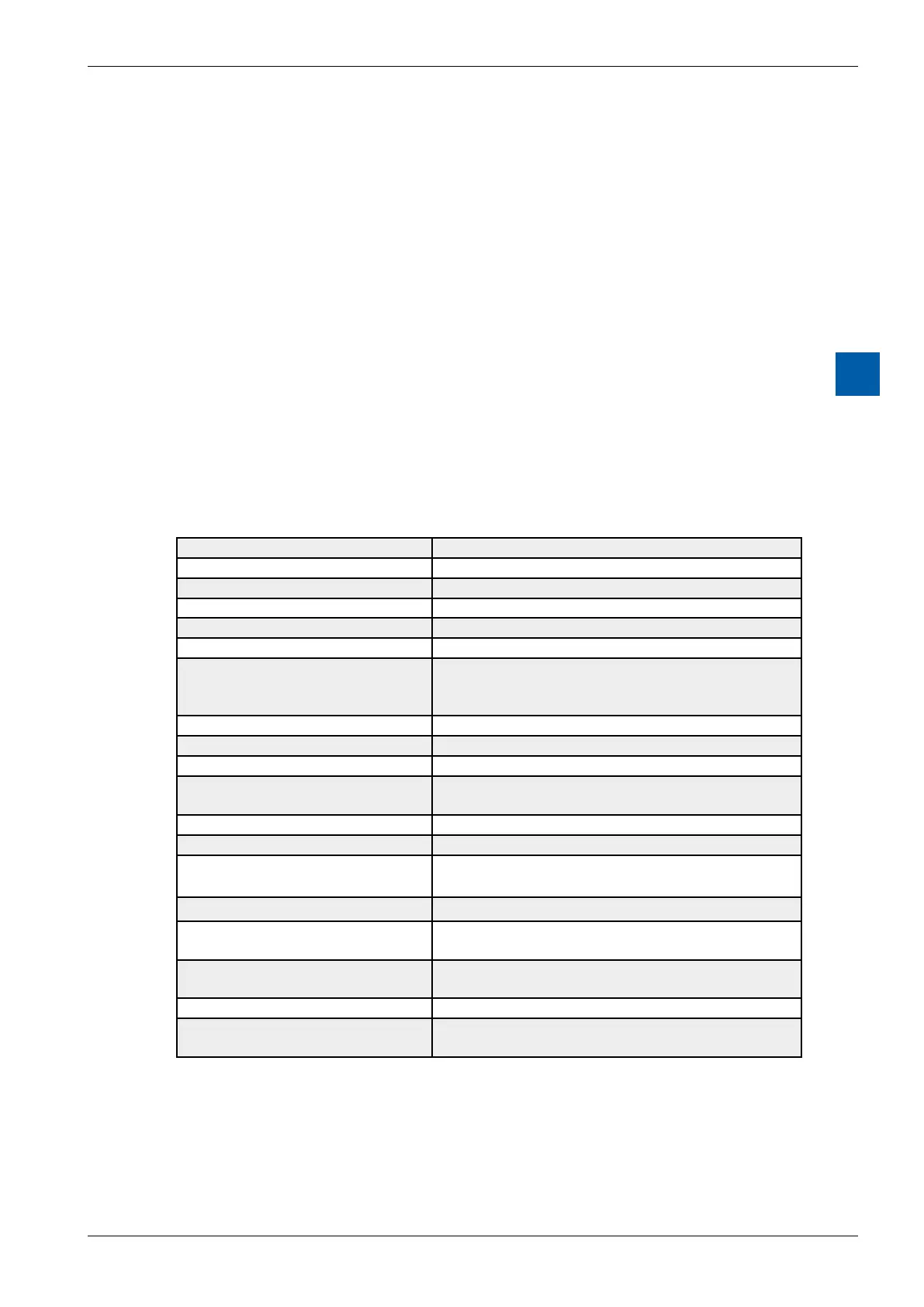

Technical data

Signal ranges see module overview

Galvanic separation no

Resolution (digital representation) 12bits(0 … 4095)

Measuring principle dierential

Conversion time ≤30µs

Input resistance W100:>10MΩ W105:100Ω/0.1%

Accuracy at 25 °C

(of measured value)

W100: ± 0.1 % + ± 1 LSB bipolar

W100: ± 0.05 % + ± 1 LSB unipolar

W105: ± 0.2 % + ± 1 LSB unip/bip.

Repeating accuracy ± 1 LSB

Common mode range (CMR) W100: ± 11 V W105: ± 8 V

Common mode rejection (CMRR) > 70 dB

Temperatureerror(0 … +55°C) W100: ± 0.2 % + ± 2 LSB

W105: ± 0.3 % + ± 2 LSB

Overvoltage protection (W100) ± 60 VDC (permanent)

Overcurrent protection (W105) ± 50 mA (permanent)

Burst protection

capacitive coupling (IEC 801-4)

± 1 kV, with unshielded cables

± 2 kV, with shielded cables

Timeconstantofinputlter 3 ms

Internal current consumption:

(from +5 V bus)

45 mA

typ. 20 mA

Internal current consumption:

(from V+ bus)

15 mA

External current consumption: 0 mA

Terminals: Pluggable 10-pole screw terminal block

(4 405 4847 0), for wires up to 1.5 mm²

Loading...

Loading...