Functions

2.19 Impedance Protection (ANSI 21)

SIPROTEC, 7UM62, Manual

C53000-G1176-C149-7, Release date 03.2010

155

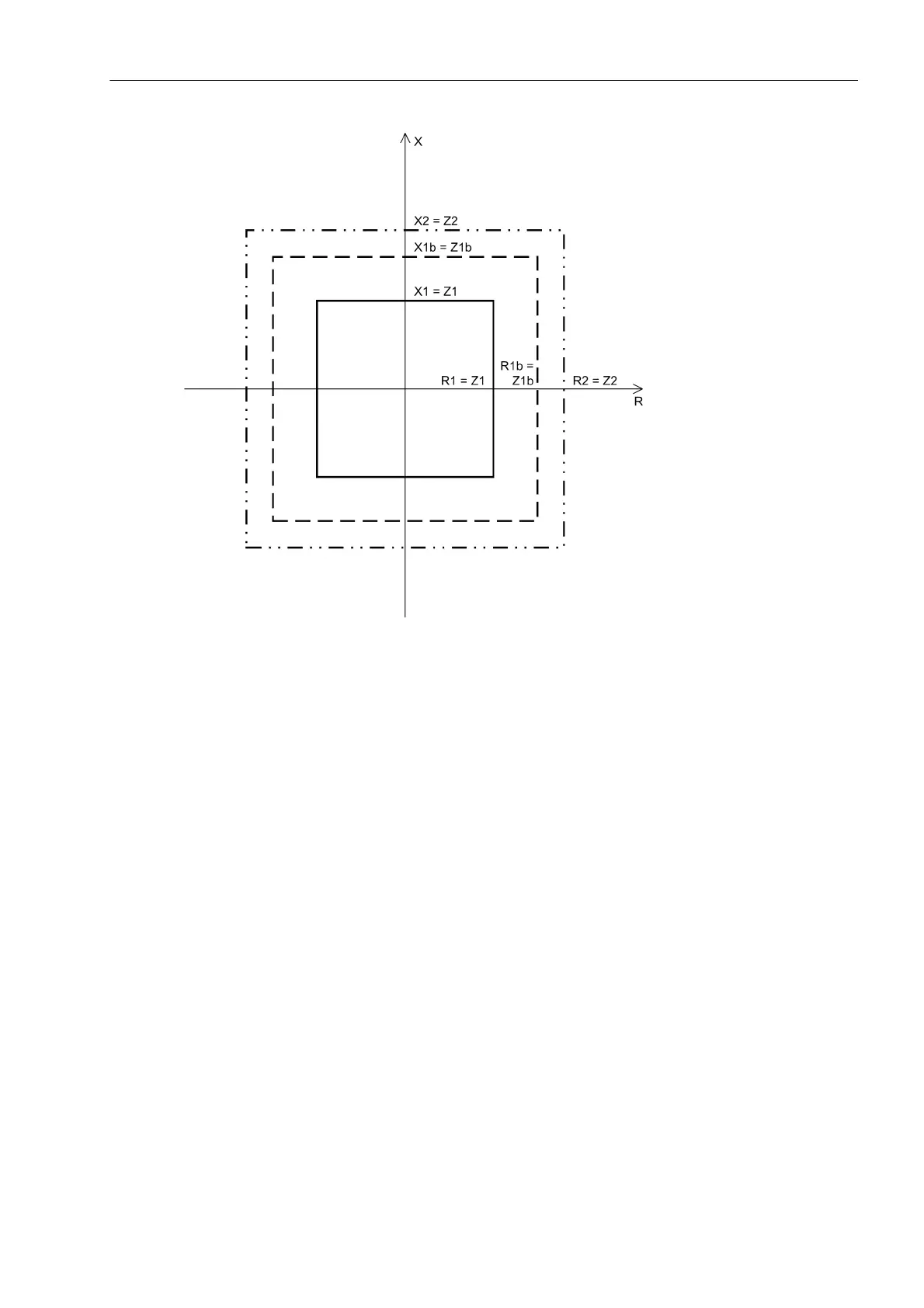

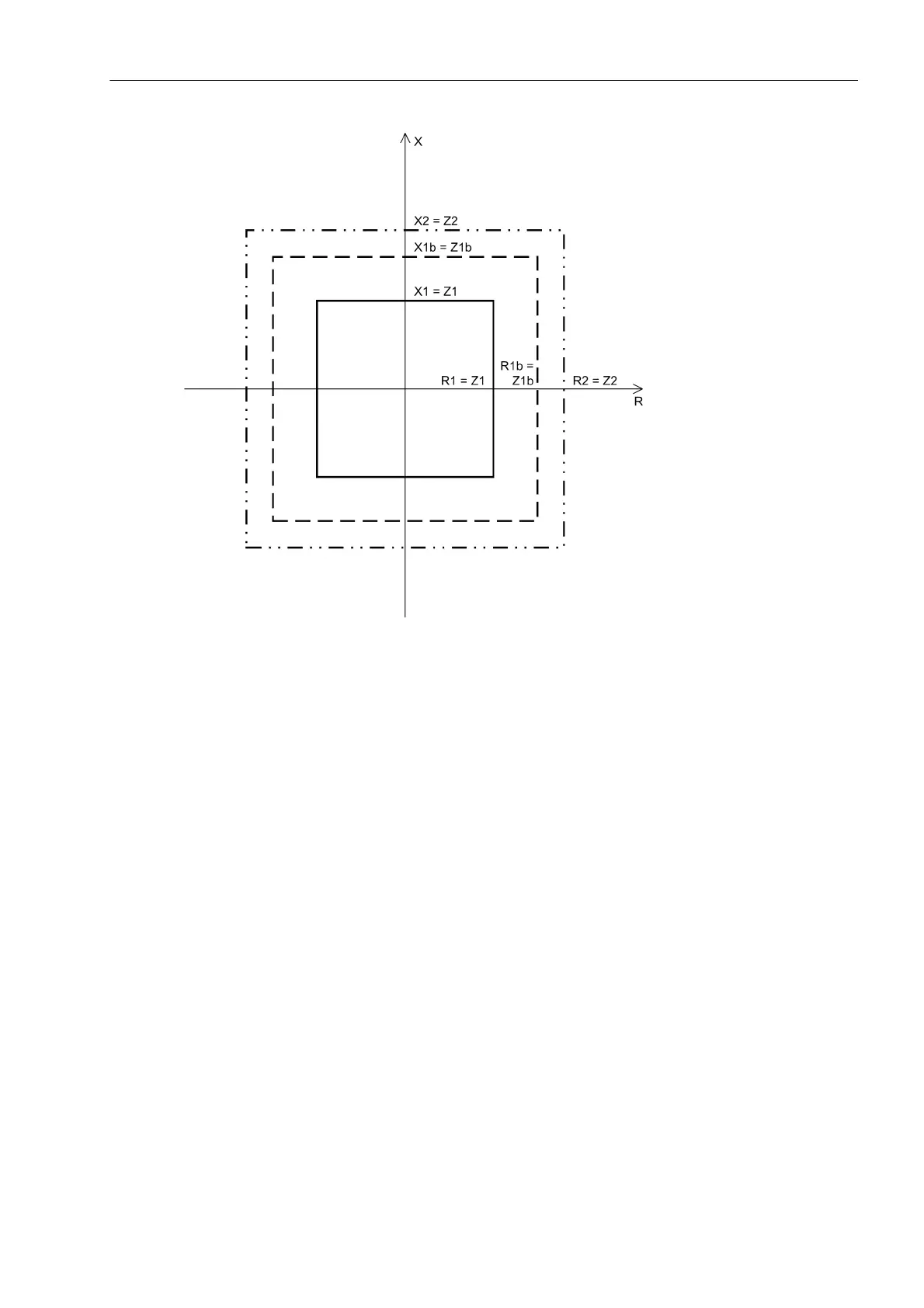

Figure 2-62 Tripping Characteristics of the Impedance Protection

Tripping Logic

The T END time delay is started subsequent to the protection pickup, establishing the fault loop. The loop im-

pedance components are compared with the limit values of the zones previously set. The tripping is executed

if the impedance is within its zone during the course of the corresponding time stage.

For the first Z1 zone and also for the Z1B overreach zone, the time delay will in most cases be zero or at least

very short. i.e. tripping occurs as soon as it is established that the fault is within this zone.

The Z1B overreach stage can be enabled from outside, via a binary input.

For the Z2 zone which may extend into the network, a time delay is selected overreaching the first stage of the

power system protection.

A drop-out can only be caused by a drop-out of the overcurrent pickup and not by exiting the tripping polygon.

Loading...

Loading...