Lesson 1 – Analog Modules

92

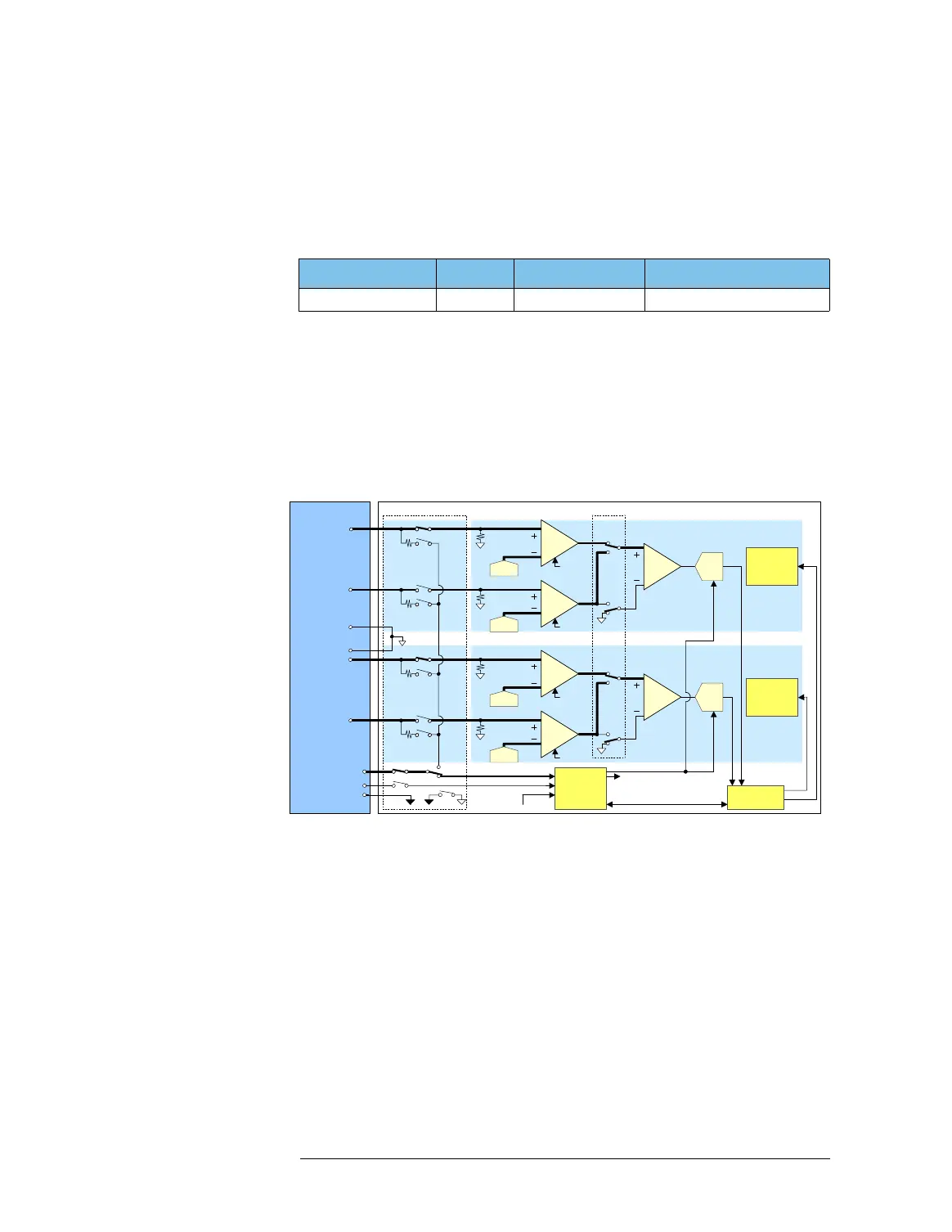

3GHz Sampler

The 3GHz Sampler (software identifier: SPB) can be used to

capture single-ended or differential repetitive waveforms up to

3 GHz with 12-bit resolution.

The 3GHz Sampler module has two identical samplers (called

sampler cores) that share the trigger/timing system and sequencer.

As shown in the following figure, the SYNC CLK pin (which is the

trigger input pin), the timing generator, and sequencer are shared

between its two sampler cores. The two sampler cores can capture

two single-ended or two differential waveforms simultaneously

with the common sampling rate, common sampling-timing, and

common sequencer program.

The one specified sampler core only can also be triggered.

3GHz Sampler (SPB) (Single-ended input routes shown with bold lines)

The two sampler cores in the module can capture two waveforms

with a very tight timing skew: around ±100 ps when the same

input range and the same normal/high-precision mode are used in

both sampler cores. To do this, on the DUT board, connect

between the sampler input pogo pads and the DUT output pins by

using coaxial cables (or printed circuit patterns) that have 50 ohm

characteristic-impedance and the same electrical length.

The 3GHz Sampler (SPB) is a single-slot analog module installed in

the testhead.

In the 3GHz Sampler, the single-ended signal or differential signal

can be captured from the pins shown in the following table.

Max. Input Frequency Resolution Sampling Rate Waveform Memory

3 GHz 12 bits 100 ksps to 10 Msps 1 M samples (per sampler core)

Input Multiplexer

CCLK Stop Seq Start

Conversion Clock (CCLK)

Core 1

Waveform

Memory

Sequencer

50

1k

ADC

S/H

Amp

50 S/H

Amp

Pogo Pin

A+ (16/Mode1)

B+ (14/Mode2)

DGND

SYNC CLK (04)

SYNC DATA (03)

C+ (12/Mode3)

D+ (10/Mode4)

AGND

(GND for SYNC CLK)

1k

AGND

Input

Amp

Master Clock

Timing

Generator

CCLK

CCLK

Input Multiplexer

Offset DAC

Offset DAC

Core 2

Waveform

Memory

50

1k

ADC

S/H

Amp

50 S/H

Amp

1k

Input

Amp

CCLK

CCLK

Offset DAC

Offset DAC

(C–)

(A–)

Loading...

Loading...