131

8331B–AVR–03/12

Atmel AVR XMEGA AU

Note: Reserved settings will not give any timeout.

• Bit 1 – ENABLE: Enable

This bit enables the WDT. Clearing this bit disables the watchdog timer.

In order to change this bit, the CEN bit in ”CTRL – Control register” on page 130 must be written

to one at the same time. This bit is protected by the configuration change protection mechanism,

For a detailed description, refer to ”Configuration Change Protection” on page 13.

• Bit 0 – CEN: Change Enable

This bit enables the ability to change the configuration of the ”CTRL – Control register” on page

130. When writing a new value to this register, this bit must be written to one at the same time for

the changes to take effect. This bit is protected by the configuration change protection mecha-

nism. For a detailed description, refer to ”Configuration Change Protection” on page 13.

11.7.2 WINCTRL – Window Mode Control register

• Bit 7:6 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 5:2 – WPER[3:0]: Window Mode Timeout Period

These bits determine the closed window period as a number of 1kHz ULP oscillator cycles in

window mode operation. The typical different closed window periods are found in Table 11-2.

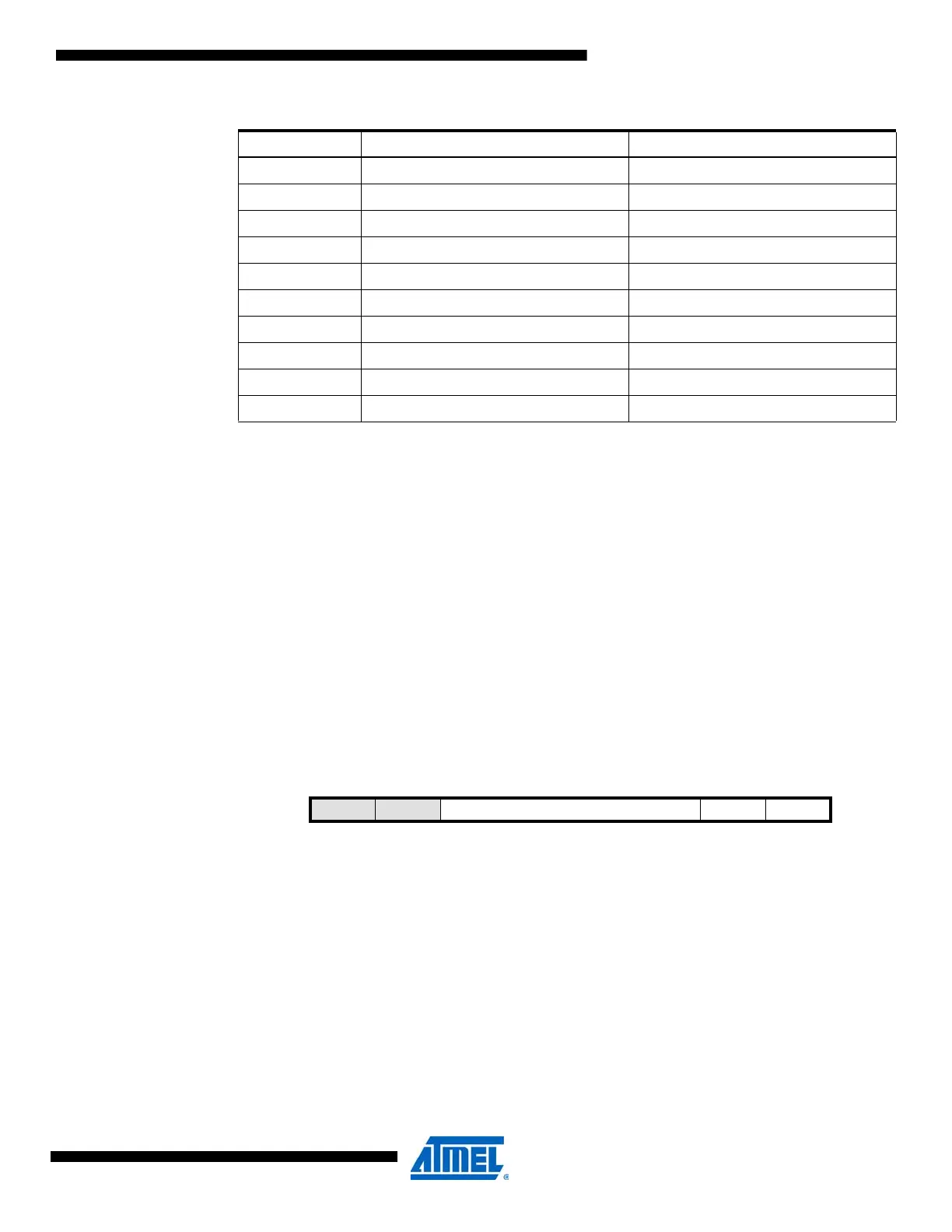

0110 512CLK 0.512s

0111 1KCLK 1.0s

1000 2KCLK 2.0s

1001 4KCLK 4.0s

1010 8KCLK 8.0s

1011 Reserved

1100 Reserved

1101 Reserved

1110 Reserved

1111 Reserved

Table 11-1. Watchdog timeout periods (Continued).

PER[3:0] Group Configuration Typical Timeout Periods

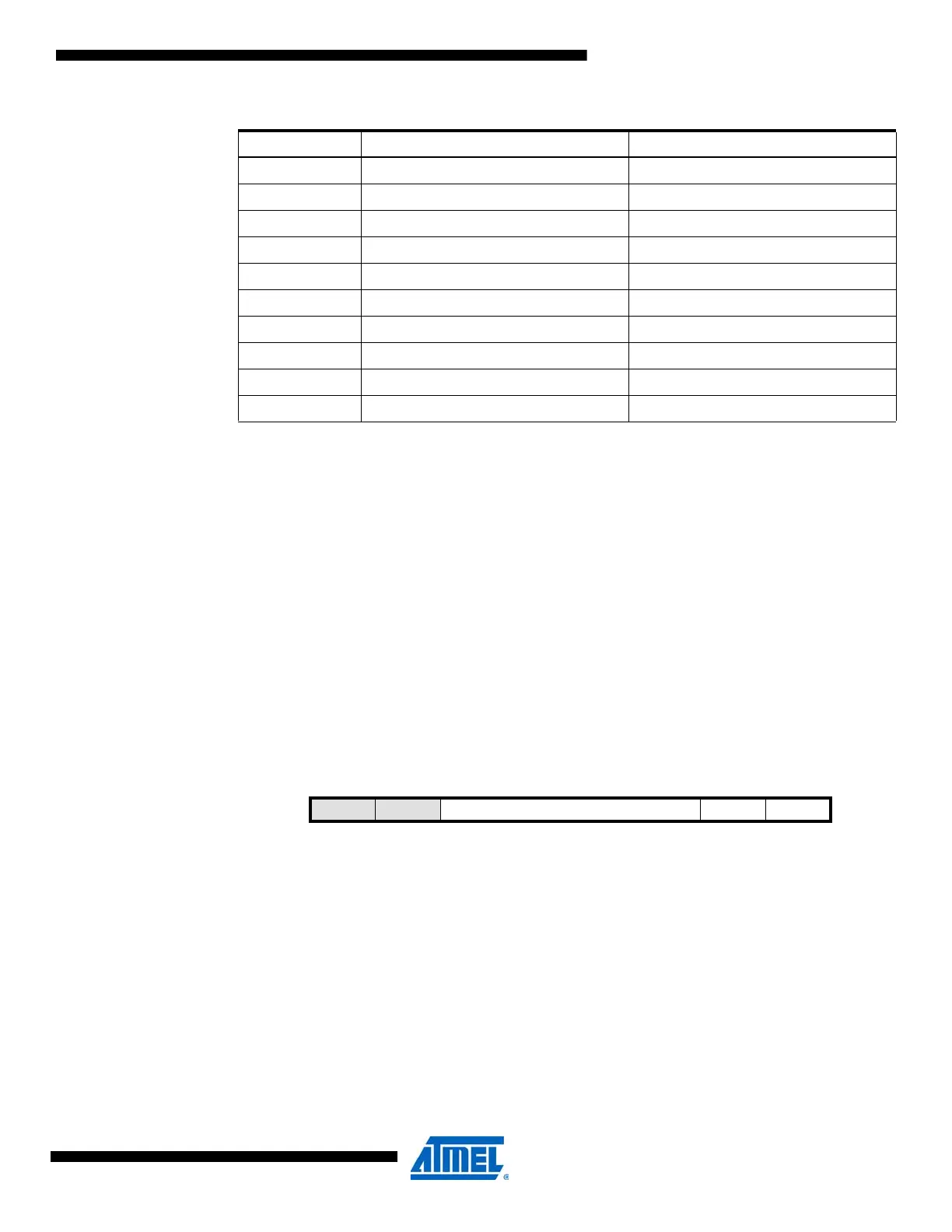

Bit 76543210

+0x01 – – WPER[3:0] WEN WCEN WINCTRL

Read/Write

(unlocked)

R R R/W R/W R/W R/W R/W R/W

Read/Write

(locked)

RRRRRRR/WR/W

Initial Value

(x = fuse)

00XXXXX0

Loading...

Loading...