255

8331B–AVR–03/12

Atmel AVR XMEGA AU

20.14 Register Description – USB Endpoint

Each of the 16 endpoint addresses have one input and one output endpoint. Each endpoint has

eight bytes of configuration/status data located in internal SRAM.

The address to the first configuration byte is (EPPTR[15:0] + 16 × endpoint address) for output

endpoints and (EPPTR[15:0] + 16 × endpoint address + 8) for input endpoints.

Some bit locations have different functions, depending on endpoint configuration type or direc-

tion, and this is reflected by using two different names for the bit locations.

20.14.1 STATUS – Status register

Note: 1. For isochronous endpoints.

• Bit 7 – STALL: STALL Flag

This flag is set when an IN or OUT transaction has been responded to with a STALL handshake.

This flag is cleared by writing a one to its bit location.

• Bit 7 – CRC: CRC Error Flag

This flag is set for isochronous output endpoints when a CRC error has been detected in an

incoming data packet. This flag is cleared by writing a one to its bit location.

• Bit 6 – UNF/OVF: Underflow/Overflow Flag

UNF: For input endpoints, the UNF flag is set when an input endpoint is not ready to send

data to the host in response of an IN token.

OVF: For output endpoints, the OVF flag is set when an output endpoint is not ready to

accept data from the host following an OUT token.

• Bit 5 – TRNCOMPL0: Transaction Complete Flag

This flag is set when an IN or OUT transaction has completed successfully. This flag is cleared

by writing a one to its bit location.

• Bit 4 – SETUP: SETUP Transaction Complete Flag

This flag is set when a SETUP, IN, or OUT transaction has completed successfully. This flag is

cleared by writing a one to its bit location.

• Bit 4 – TRNCOMPL1: Transaction Complete Flag

This flag is set when a SETUP, IN, or OUT transaction has completed successfully. This flag is

cleared by writing a one to its bit location.

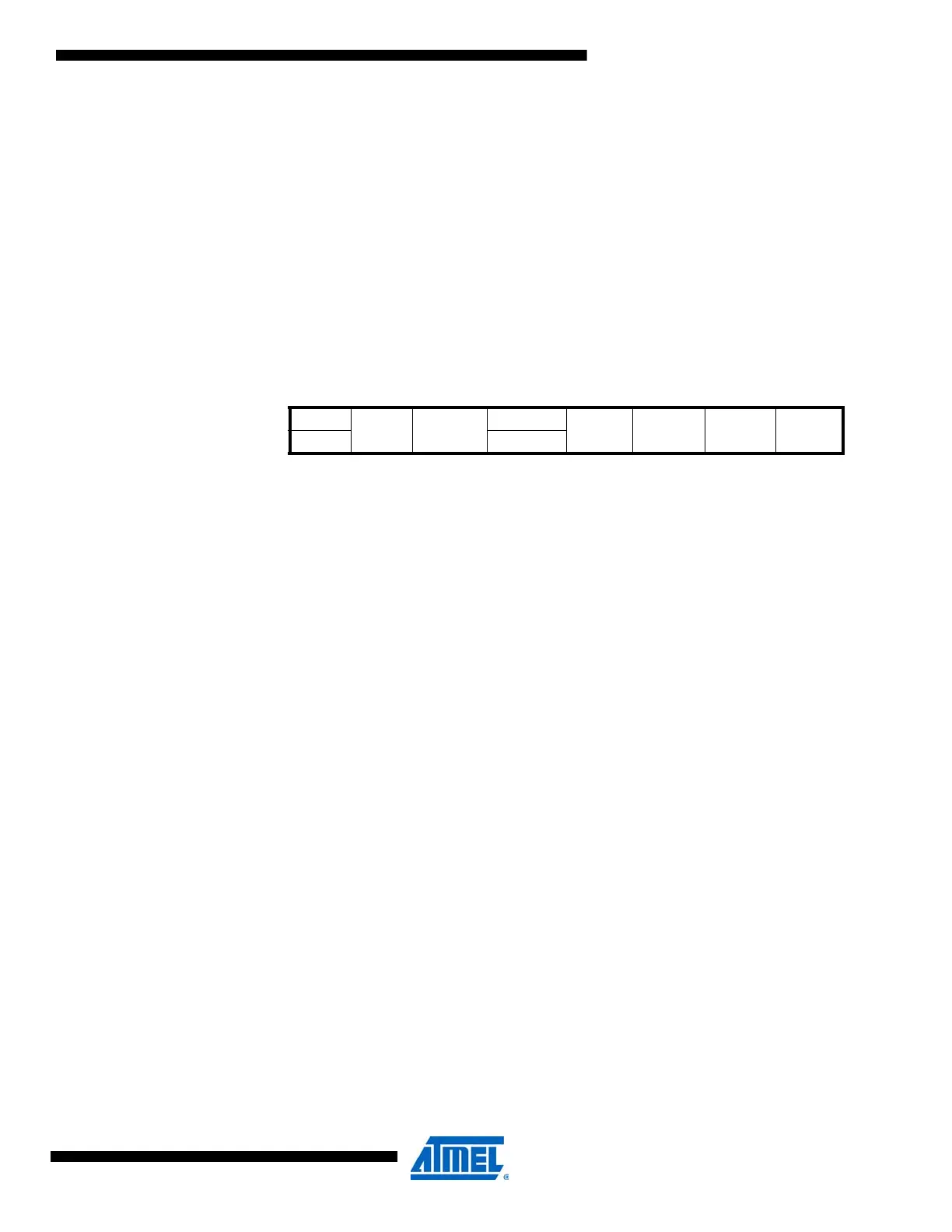

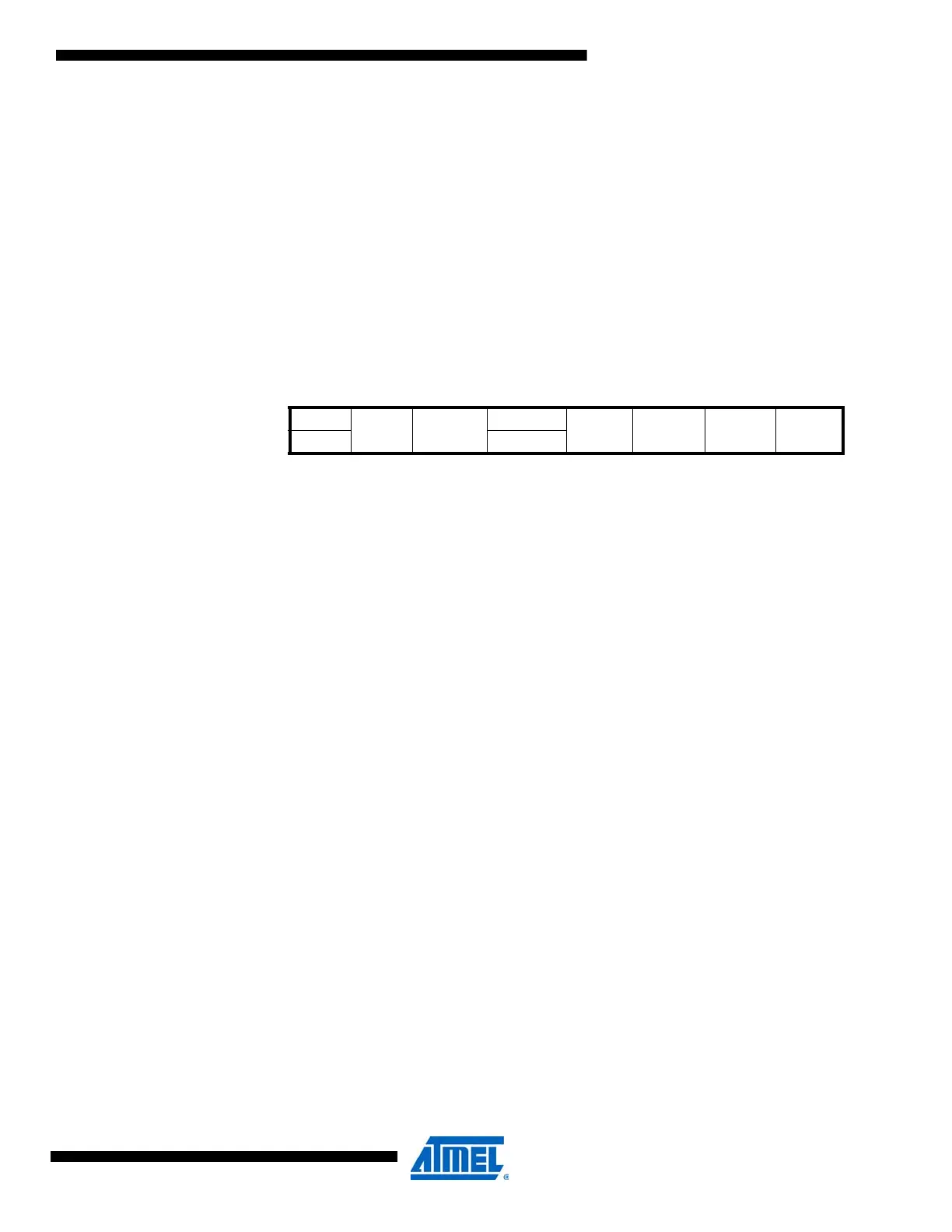

Bit 7 6 5 4 3 2 1 0

+0x00

STALL

UNF/ OVF TRNCOMPL0

SETUP

BANK BUSNACK1 BUSNACK0 TOGGLE STATUS

CRC

(1)

TRNCOMPL1

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value 0 0 0 0 0 0 0 0

Loading...

Loading...