88

8331B–AVR–03/12

Atmel AVR XMEGA AU

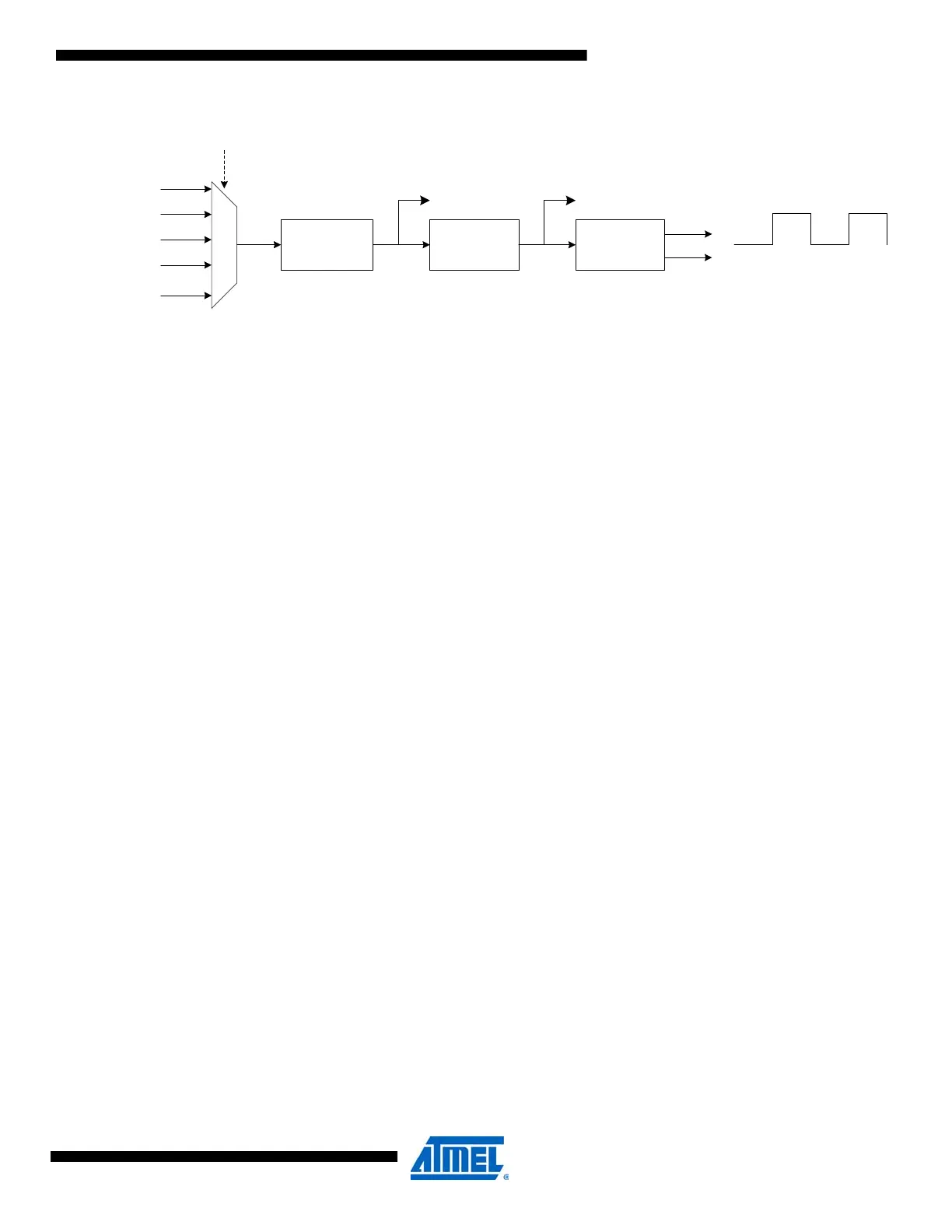

Figure 7-5. System clock selection and prescalers.

Prescaler A divides the system clock, and the resulting clock is clk

PER4

. Prescalers B and C can

be enabled to divide the clock speed further to enable peripheral modules to run at twice or four

times the CPU clock frequency. If Prescalers B and C are not used, all the clocks will run at the

same frequency as the output from Prescaler A.

The system clock selection and prescaler registers are protected by the configuration change

protection mechanism, employing a timed write procedure for changing the system clock and

prescaler settings. For details, refer to ”Configuration Change Protection” on page 13.

7.6 PLL with 1x-31x Multiplication Factor

The built-in phase locked loop (PLL) can be used to generate a high-frequency system clock.

The PLL has a user-selectable multiplication factor of from 1 to 31. The output frequency, f

OUT

, is

given by the input frequency, f

IN

, multiplied by the multiplication factor, PLL_FAC.

Four different clock sources can be chosen as input to the PLL:

• 2MHz internal oscillator

• 32MHz internal oscillator divided by 4

• 0.4MHz - 16MHz crystal oscillator

• External clock

To enable the PLL, the following procedure must be followed:

1. Enable reference clock source.

2. Set the multiplication factor and select the clock reference for the PLL.

3. Wait until the clock reference source is stable.

4. Enable the PLL.

Hardware ensures that the PLL configuration cannot be changed when the PLL is in use. The

PLL must be disabled before a new configuration can be written.

It is not possible to use the PLL before the selected clock source is stable and the PLL has

locked.

The reference clock source cannot be disabled while the PLL is running.

Prescaler A

1, 2, 4, ... , 512

Prescaler B

1, 2, 4

Prescaler C

1, 2

Internal 2MHz Osc.

Internal 32.768kHz Osc.

Internal 32MHz Osc.

External Oscillator or Clock.

Clk

CPU

Clock Selection

Clk

PER

Clk

SYS

Clk

PER2

Clk

PER4

Internal PLL.

Loading...

Loading...