355

8331B–AVR–03/12

Atmel AVR XMEGA AU

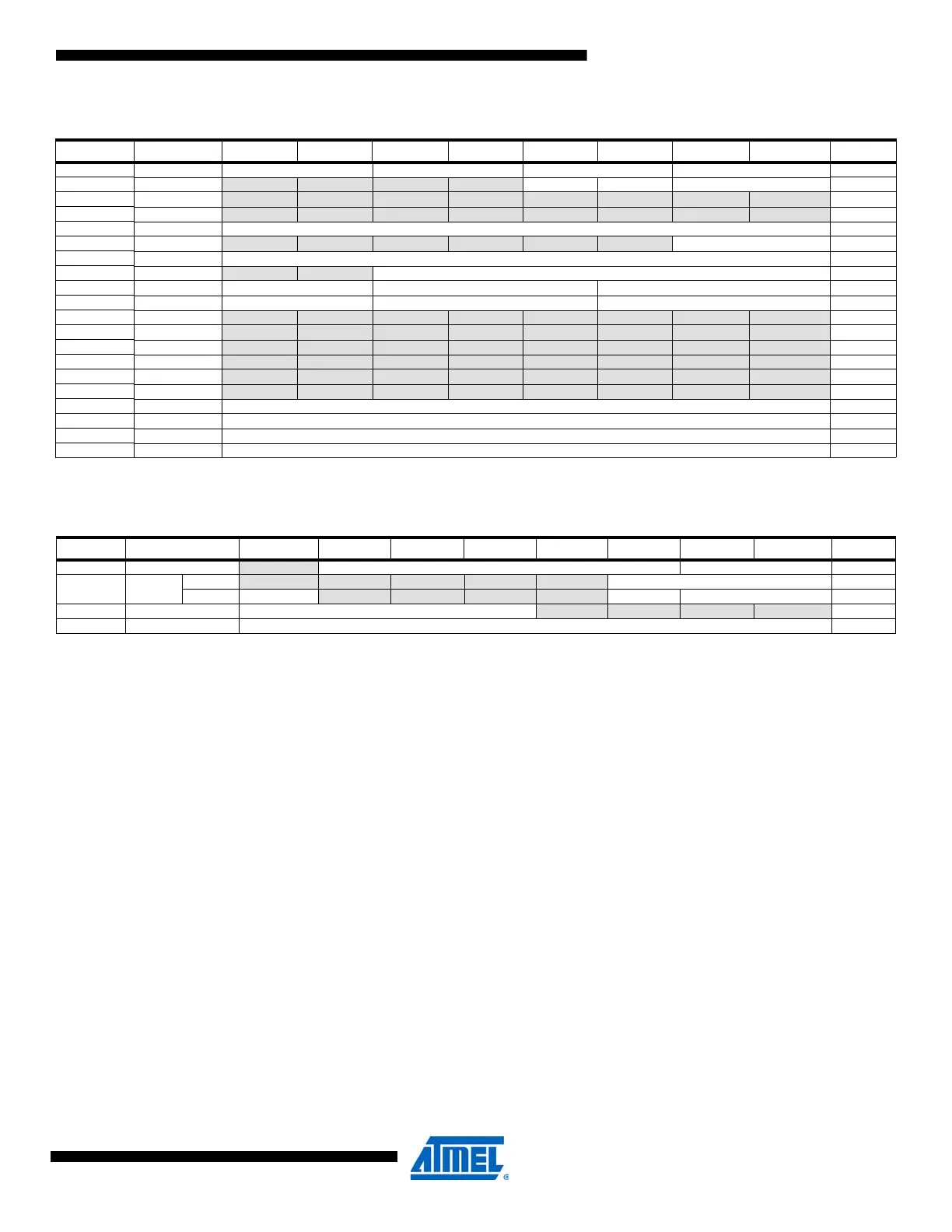

27.12 Register Summary - EBI

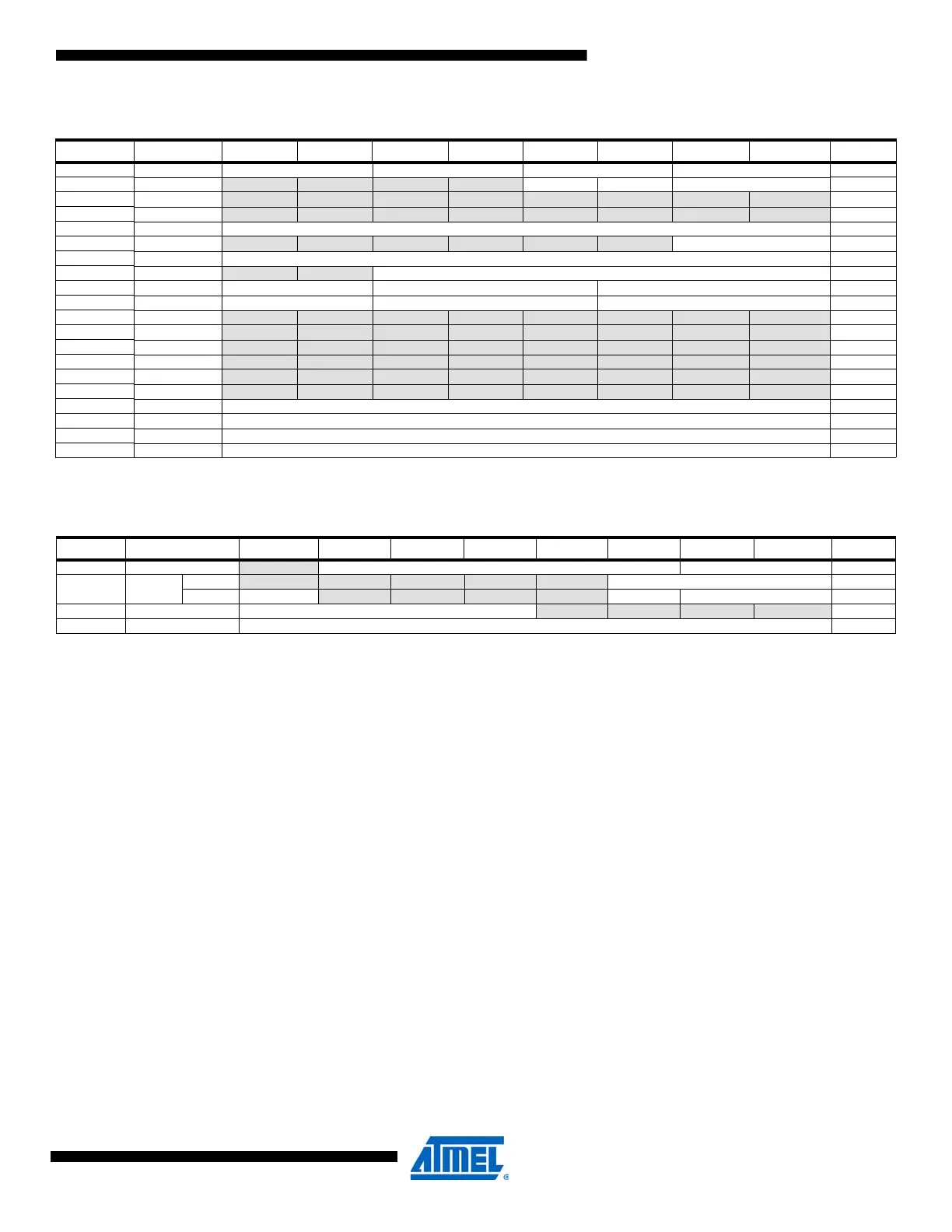

27.13 Register Summary - EBI Chip Select

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

+0x00 CTRL SDDATAW[1:0] LPCMODE[1:0] SRMODE[1:0] IFMODE[1:0] 346

+0x01 SDRAMCTRLA – – – – SDCAS SDROW SDCOL[1:0] 347

+0x02 Reserved – – – – – – – –

+0x03 Reserved – – – – – – – –

+0x04 REFRESHL SDRAM Refresh Period Low Byte 348

+0x05 REFRESHH – – – – – – SDRAM Refresh Period High 348

+0x06 INITDLYL SDRAM Initialization Time Low Byte 348

+0x07 INITDLYH – – SDRAM Initialization Time High Byte 348

+0x08 SDRAMCTRLB MRDLY[1:0] ROWCYCDLY[[2:0] RPDLY[2:0] 349

+0x09 SDRAMCTRLC WRDLY[1:0] ESRDLY[2:0] ROWCOLDLY[2:0] 350

+0x0A Reserved – – – – – – – –

+0x0B Reserved – – – – – – – –

+0x0C Reserved – – – – – – – –

+0x0D Reserved – – – – – – – –

+0x0E Reserved – – – – – – – –

+0x0F Reserved – – – – – – – –

+0x10 CS0 Chip Select 0 Offset Address

+0x14 CS1 Chip Select 1 Offset Address

+0x18 CS2 Chip Select 2 Offset Address

+0x1C CS3 Chip Select 3 Offset Address

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

+0x00 CTRLA – ASIZE[4:0] MODE[1:0] 351

+0x01 CTRLB (SRAM) – – – – – SRWS[2:0] 353

(SDRAM) SDINITDONE – – – – SDSREN SDMODE[1:0] 353

+0x02 BASEADDRL Chip Select Base Address Low Byte – – – –354

+0x03 BASEADDRH Chip Select Base Address High Byte 354

Loading...

Loading...