348

8331B–AVR–03/12

Atmel AVR XMEGA AU

27.10.3 REFRESH – SDRAM Refresh Period Register

• Bit 15:10 – Reserved

These bits are unused and reserved for future use.

• Bit 9:0 – REFRESH[9:0]: SDRAM Refresh Period

This register sets the refresh period as a number of Clk

PER2

cycles. If the EBI is busy with

another external memory access at time of refresh, up to 4 refresh will be remembered and

given at the first available time.

27.10.4 INITDLY – SDRAM Initialization Delay register

• Bit 15:14 – Reserved

These bits are unused and reserved for future use.

Table 27-14. SDRAM column bits.

SDCOL[1:0] Group Configuration Description

00 8BIT 8 column bits

01 9BIT 9 column bits

10 10BIT 10 column bits

11 11BIT 11 column bits

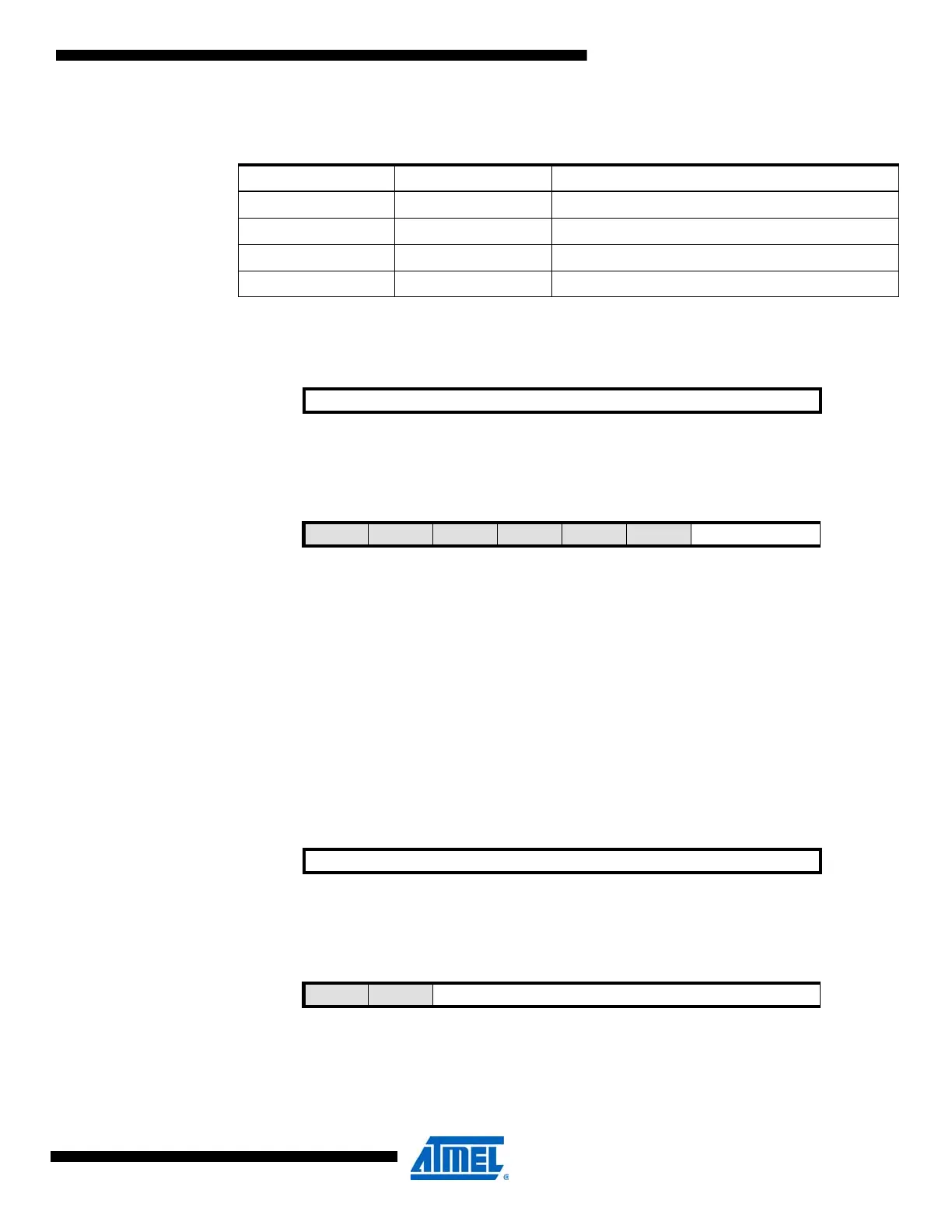

Bit 76543210

+0x04 REFRESH[7:0] REFRESHL

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value

00000000

Bit 76543210

+0x05 – – – – – – REFRESH[9-8] REFRESHH

Read/WriteRRRRRRR/WR/W

Initial Value

00000000

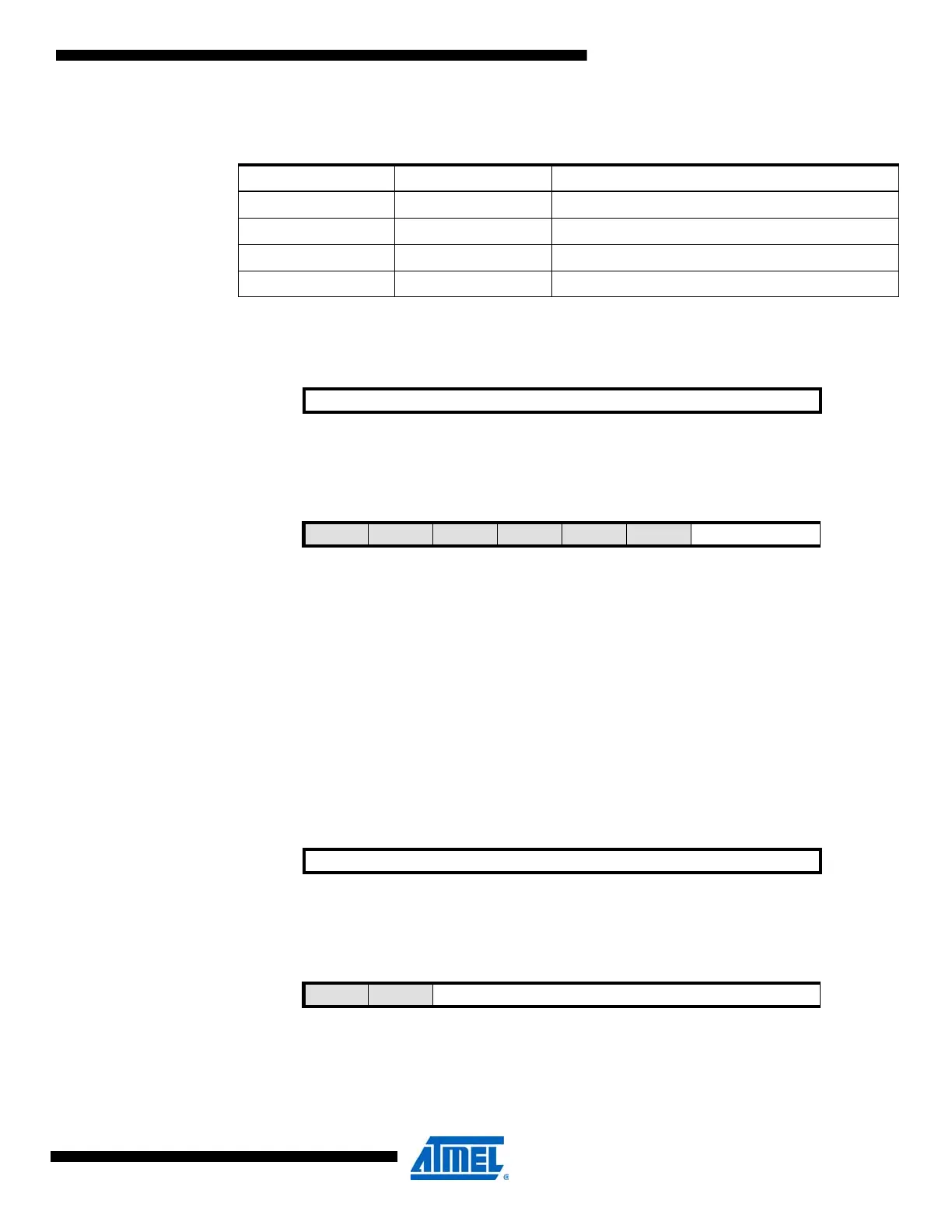

Bit 76543210

+0x06 INITDLY[7:0] INTDLYL

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value

00000000

Bit 76543210

+0x07 – – INITDLY[13-8] INITDLYH

Read/Write R R R/W R/W R/W R/W R/W R/W

Initial Value

00000000

Loading...

Loading...