70

8331B–AVR–03/12

Atmel AVR XMEGA AU

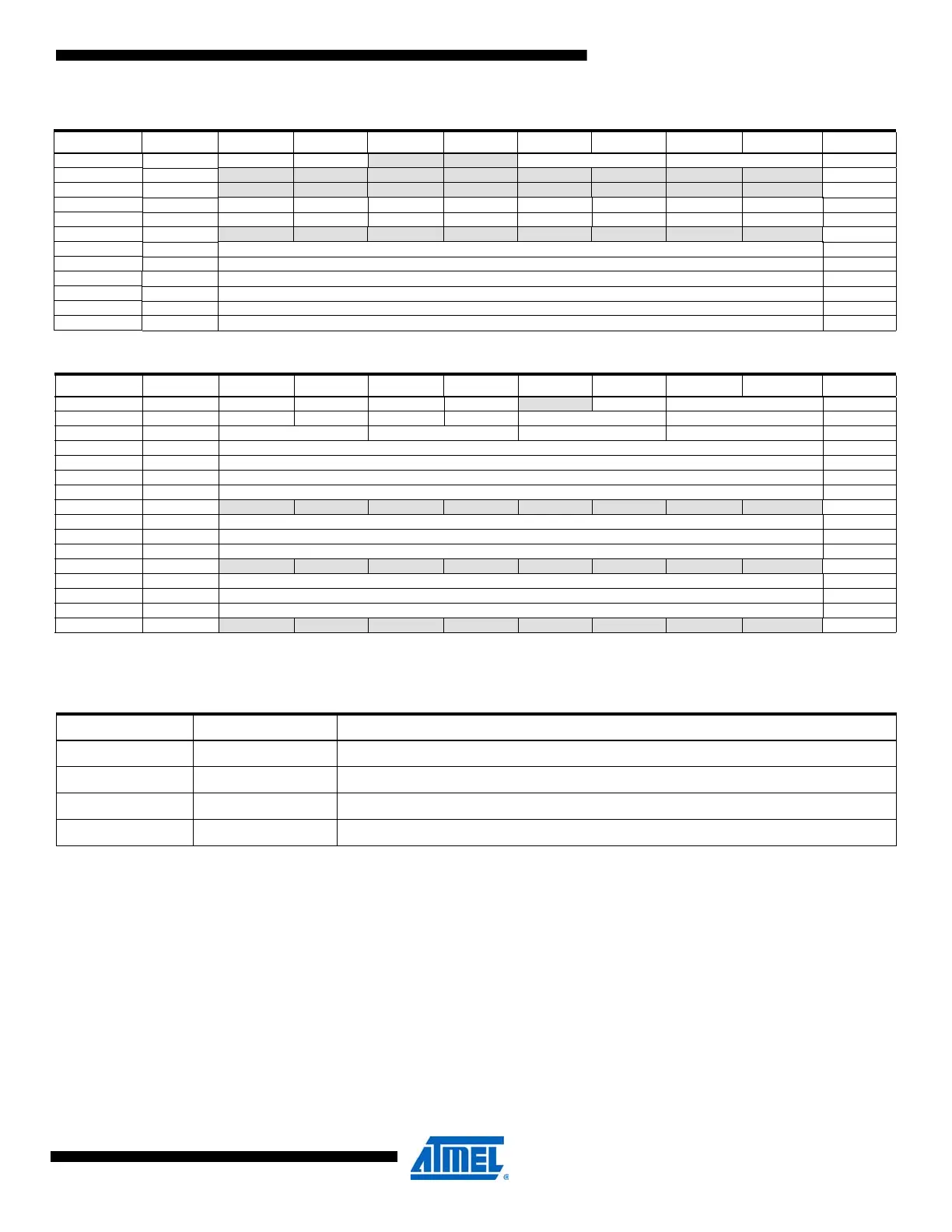

5.15 Register Summary – DMA Controller

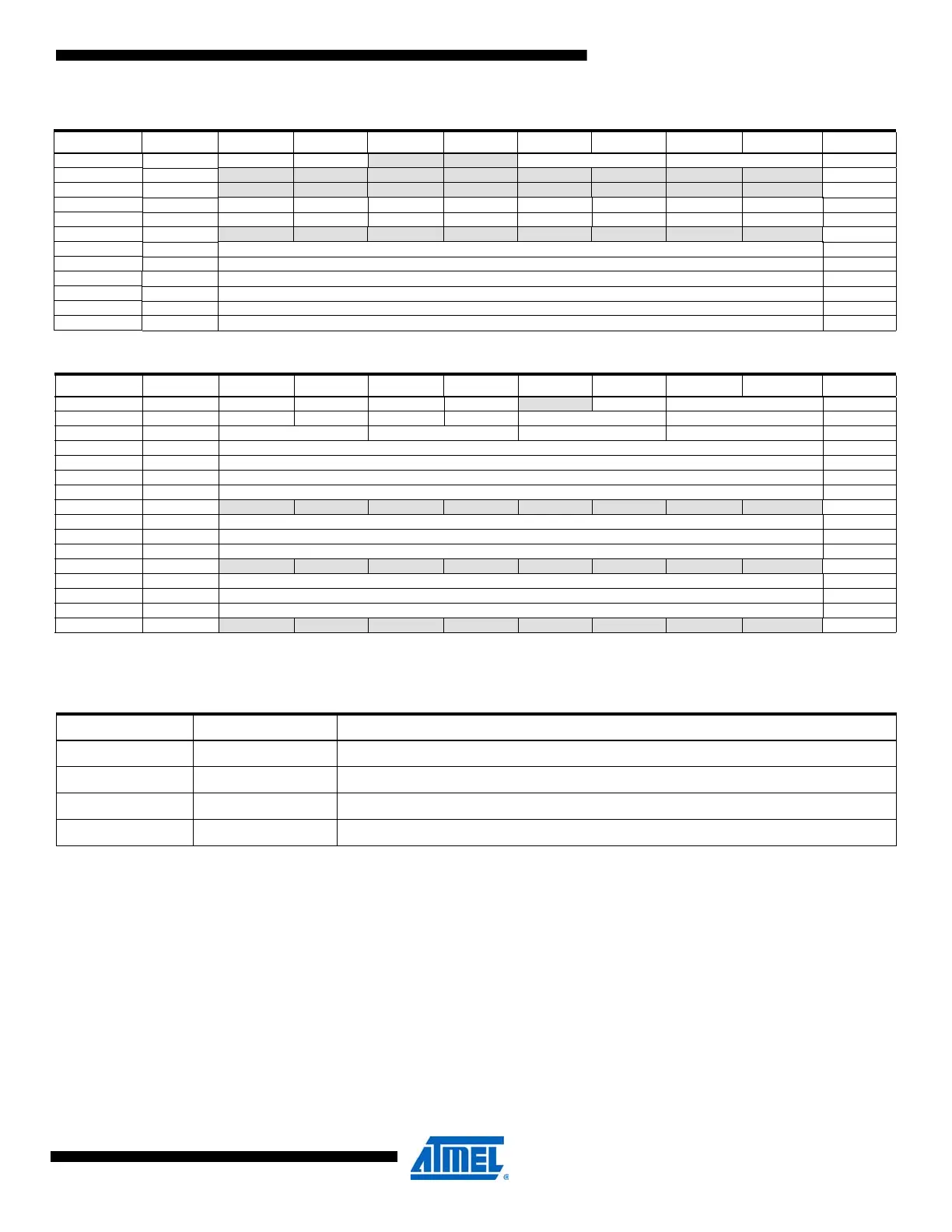

5.16 Register Summary – DMA Channel

5.17 DMA Interrupt Vector Summary

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

+0x00 CTRL ENABLE RESET - - DBUFMODE[1:0] PRIMODE[1:0] 59

+0x01 Reserved – – – – – – – –

+0x02 Reserved – – – – – – – –

+0x03 INTFLAGS CH3ERRIF CH2ERRIF CH1ERRIF CH0ERRIF CH3TRNFIF CH2TRNFIF CH1TRNFIF CH0TRNFIF 60

+0x04 STATUS CH3BUSY CH2BUSY CH1BUSY CH0BUSY CH3PEND CH2PEND CH1PEND CH0PEND 60

+0x05 Reserved – – – – – – – –

+0x06 TEMPL TEMP[7:0] 60

+0x07 TEMPH TEMP[15:8] 61

+0x10 CH0 Offset Offset address for DMA Channel 0

+0x20 CH1 Offset Offset address for DMA Channel 1

+0x30 CH2 Offset Offset address for DMA Channel 2

+0x40 CH3 Offset Offset address for DMA Channel 3

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

+0x00 CTRLA ENABLE RESET REPEAT TRFREQ - SINGLE BURSTLEN[1:0] 61

+0x01 CTRLB CHBUSY CHPEND ERRIF TRNIF ERRINTLVL[1:0] TRNINTLVL[1:0] 63

+0x02 ADDCTRL SRCRELOAD[1:0] SRCDIR[1:0] DESTRELOAD[1:0] DESTDIR[1:0] 63

+0x03 TRIGSRC TRIGSRC[7:0] 65

+0x04 TRFCNTL TRFCNT[7:0] 67

+0x05 TRFCNTH TRFCNT[15:8] 67

+0x06 REPCNT REPCNT[7:0] 68

+0x07 Reserved – – – – – – – –

+0x08 SRCADDR0 SRCADDR[7:0] 68

+0x09 SRCADDR1 SRCADDR[15:8] 68

+0x0A SRCADDR2 SRCADDR[23:16] 68

+0x0B Reserved – – – – – – – –

+0x0C DESTADDR0 DESTADDR[7:0] 69

+0x0D DESTADDR1 DESTADDR[15:8] 69

+0x0E DESTADDR2 DESTADDR[23:16] 69

+0x0F Reserved – – – – – – – –

Table 5-14. DMA interrupt vectors and their word offset addresses from the DMA controller interrupt base.

Offset Source Interrupt Description

0x00 CH0_vect DMA controller channel 0 interrupt vector

0x02 CH1_vect DMA controller channel 1 interrupt vector

0x04 CH2_vect DMA controller channel 2 interrupt vector

0x06 CH3_vect DMA controller channel 3 interrupt vector

Loading...

Loading...