56

8331B–AVR–03/12

Atmel AVR XMEGA AU

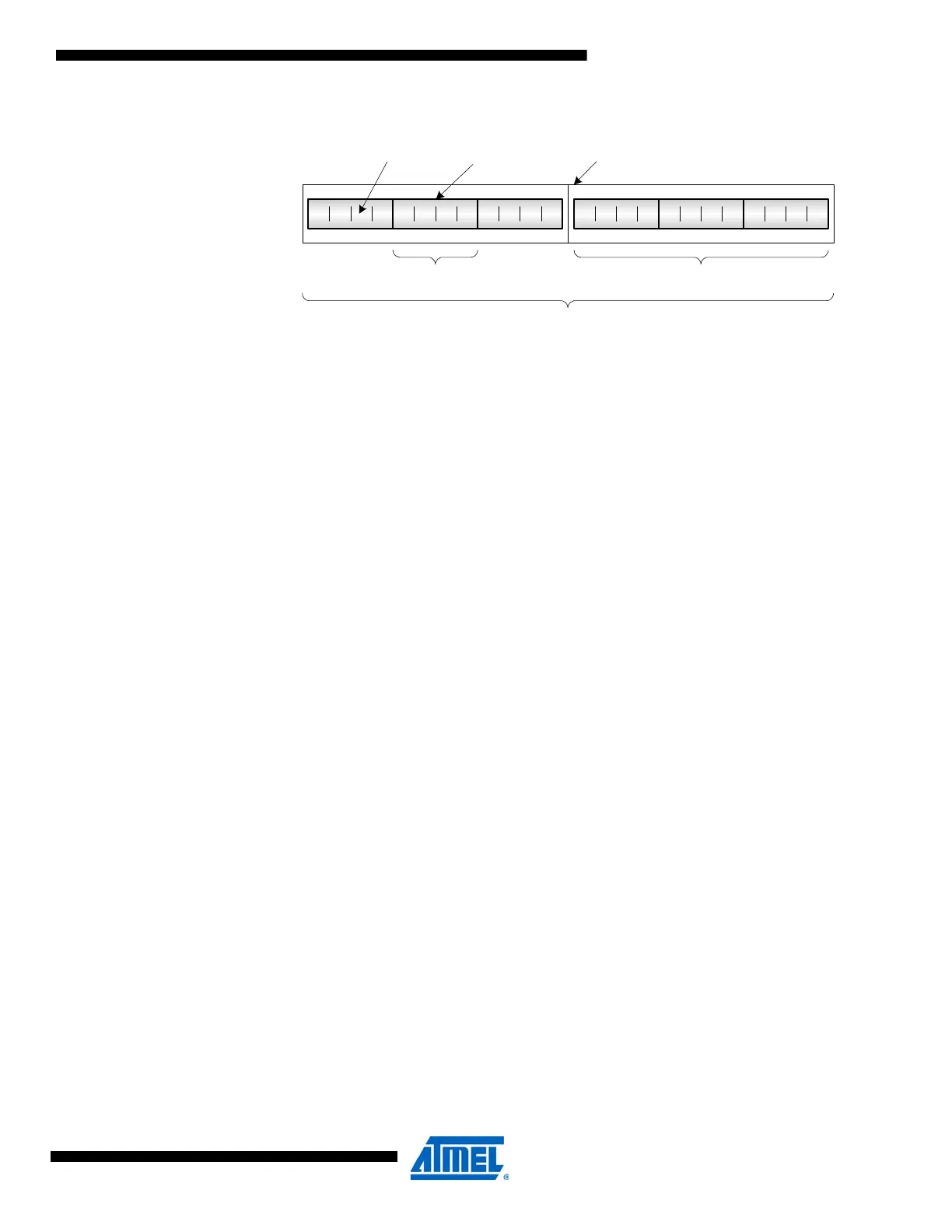

Figure 5-2. DMA transaction.

5.4 Transfer Triggers

DMA transfers can be started only when a DMA transfer request is detected. A transfer request

can be triggered from software, from an external trigger source (peripheral), or from an event.

There are dedicated source trigger selections for each DMA channel. The available trigger

sources may vary from device to device, depending on the modules or peripherals that exist in

the device. Using a transfer trigger for a module or peripherals that does not exist will have no

effect. For a list of all transfer triggers, refer to ”TRIGSRC – Trigger Source” on page 65.

By default, a trigger starts a block transfer operation. When the block transfer is complete, the

channel is automatically disabled. When enabled again, the channel will wait for the next block

transfer trigger. It is possible to select the trigger to start a burst transfer instead of a block trans-

fer. This is called a single-shot transfer, and for each trigger only one burst is transferred. When

repeat mode is enabled, the next block transfer does not require a transfer trigger. It will start as

soon as the previous block is done.

If the trigger source generates a transfer request during an ongoing transfer, this will be kept

pending, and the transfer can start when the ongoing one is done. Only one pending transfer

can be kept, and so if the trigger source generates more transfer requests when one is already

pending, these will be lost.

5.5 Addressing

The source and destination address for a DMA transfer can either be static or automatically

incremented or decremented, with individual selections for source and destination. When

address increment or decrement is used, the default behaviour is to update the address after

each access. The original source and destination addresses are stored by the DMA controller,

and so the source and destination addresses can be individually configured to be reloaded at

the following points:

• End of each burst transfer

• End of each block transfer

• End of transaction

• Never reloaded

5.6 Priority Between Channels

If several channels request a data transfer at the same time, a priority scheme is available to

determine which channel is allowed to transfer data. Application software can decide whether

Four-byte burst mode Block size: 12 bytes Repeat count: 2

Burst transfer Block transfer

DMA transaction

Loading...

Loading...