133

8331B–AVR–03/12

Atmel AVR XMEGA AU

11.7.3 STATUS – Status register

• Bit 7:1 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 0 – SYNCBUSY: Synchronization Busy Flag

This flag is set after writing to the CTRL or WINCTRL registers and the data are being synchro-

nized from the system clock to the WDT clock domain. This bit is automatically cleared after the

synchronization is finished. Synchronization will take place only when the ENABLE bit for the

Watchdog Timer is set.

11.8 Register Summary

Bit 7654321 0

+0x02 – – – – – – – SYNCBUSY STATUS

Read/Write RRRRRRR R

Initial Value 0 0 0 0 0 0 0 0

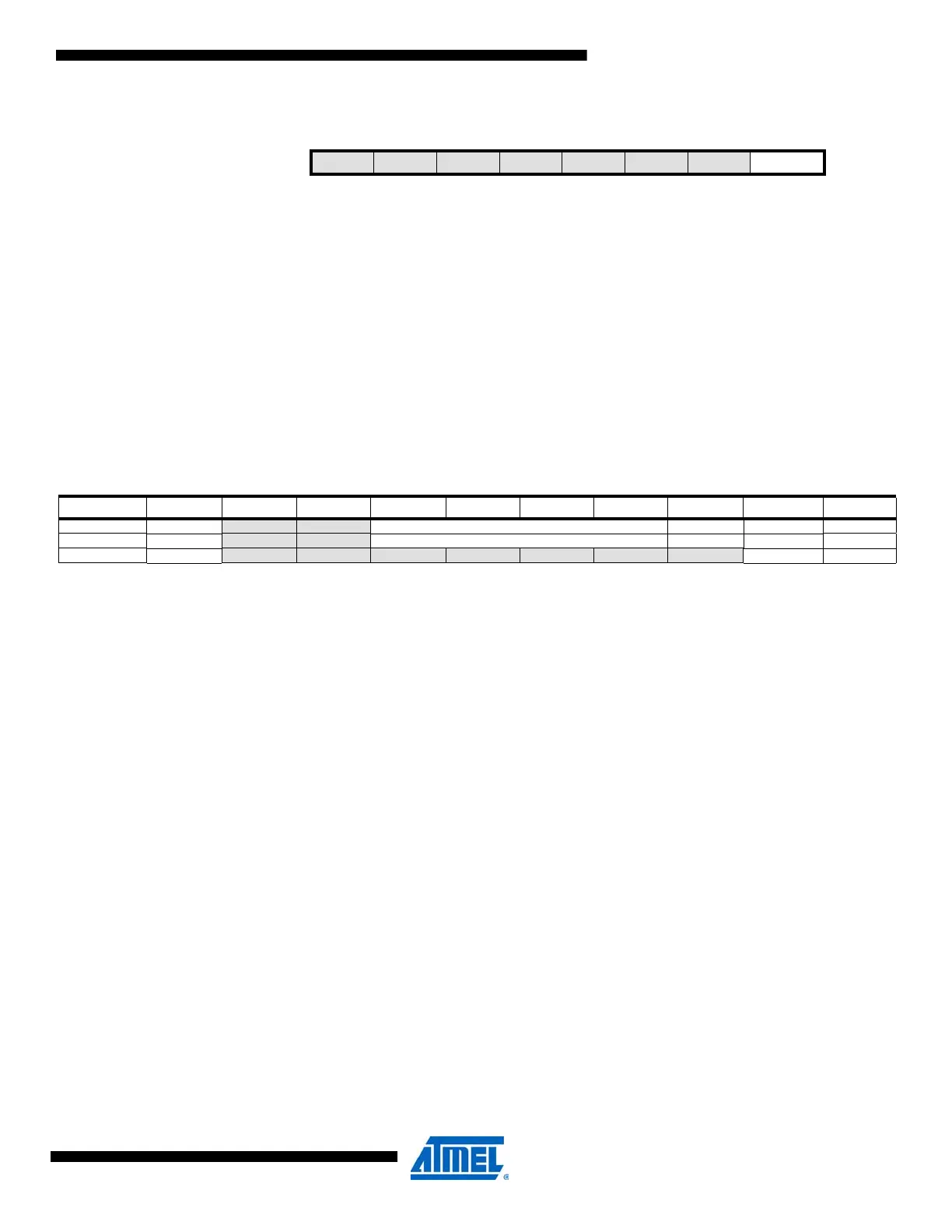

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

+0x00 CTRL – – PER[3:0] ENABLE CEN 130

+0x01 WINCTRL – – WPER[3:0] WEN WCEN 131

+0x02 STATUS – – – – – – – SYNCBUSY 133

Loading...

Loading...