280

8331B–AVR–03/12

Atmel AVR XMEGA AU

register can only be accessed when the SCL line is held low by the master; i.e., when CLKHOLD

is set.

In master write mode, writing the DATA register will trigger a data byte transfer followed by the

master receiving the acknowledge bit from the slave. WIF and CLKHOLD are set.

In master read mode, RIF and CLKHOLD are set when one byte is received in the DATA regis-

ter. If smart mode is enabled, reading the DATA register will trigger the bus operation as set by

the ACKACT bit. If a bus error occurs during reception, WIF and BUSERR are set instead of

RIF.

Accessing the DATA register will clear the master interrupt flags and CLKHOLD.

21.10 Register Description – TWI Slave

21.10.1 CTRLA – Control register A

• Bit 7:6

– INTLVL[1:0]: Interrupt Level

These bits select the interrupt level for the TWI master interrupt, as described in ”Interrupts and

Programmable Multilevel Interrupt Controller” on page 134.

•Bit 5

– DIEN: Data Interrupt Enable

Setting the data interrupt enable (DIEN) bit enables the data interrupt when the data interrupt

flag (DIF) in the STATUS register is set. The INTLVL bits must be nonzero for the interrupt to be

generated.

•Bit 4

– APIEN: Address/Stop Interrupt Enable

Setting the address/stop interrupt enable (APIEN) bit enables the address/stop interrupt when

the address/stop interrupt flag (APIF) in the STATUS register is set. The INTLVL bits must be

nonzero for interrupt to be generated.

•Bit 3

– ENABLE: Enable TWI Slave

Setting this bit enables the TWI slave.

•Bit 2

– PIEN: Stop Interrupt Enable

Setting the this bit will cause APIF in the STATUS register to be set when a STOP condition is

detected.

•Bit 1

– PMEN: Promiscuous Mode Enable

By setting the this bit, the slave address match logic responds to all received addresses. If this

bit is cleared, the address match logic uses the ADDR register to determine which address to

recognize as its own address.

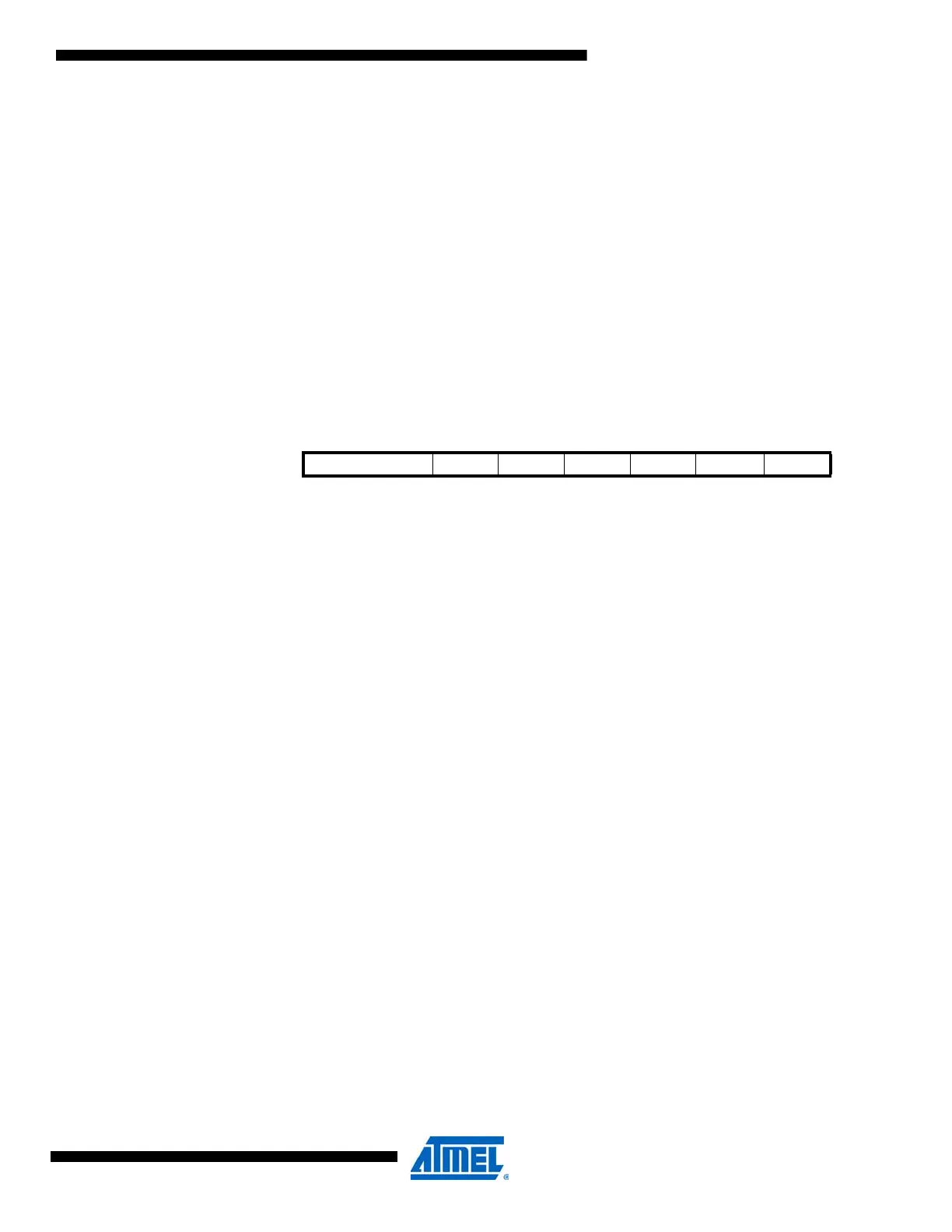

Bit 765432 1 0

+0x00 INTLVL[1:0] DIEN APIEN ENABLE PIEN PMEN SMEN CTRLA

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value000000 0 0

Loading...

Loading...