104

8331B–AVR–03/12

Atmel AVR XMEGA AU

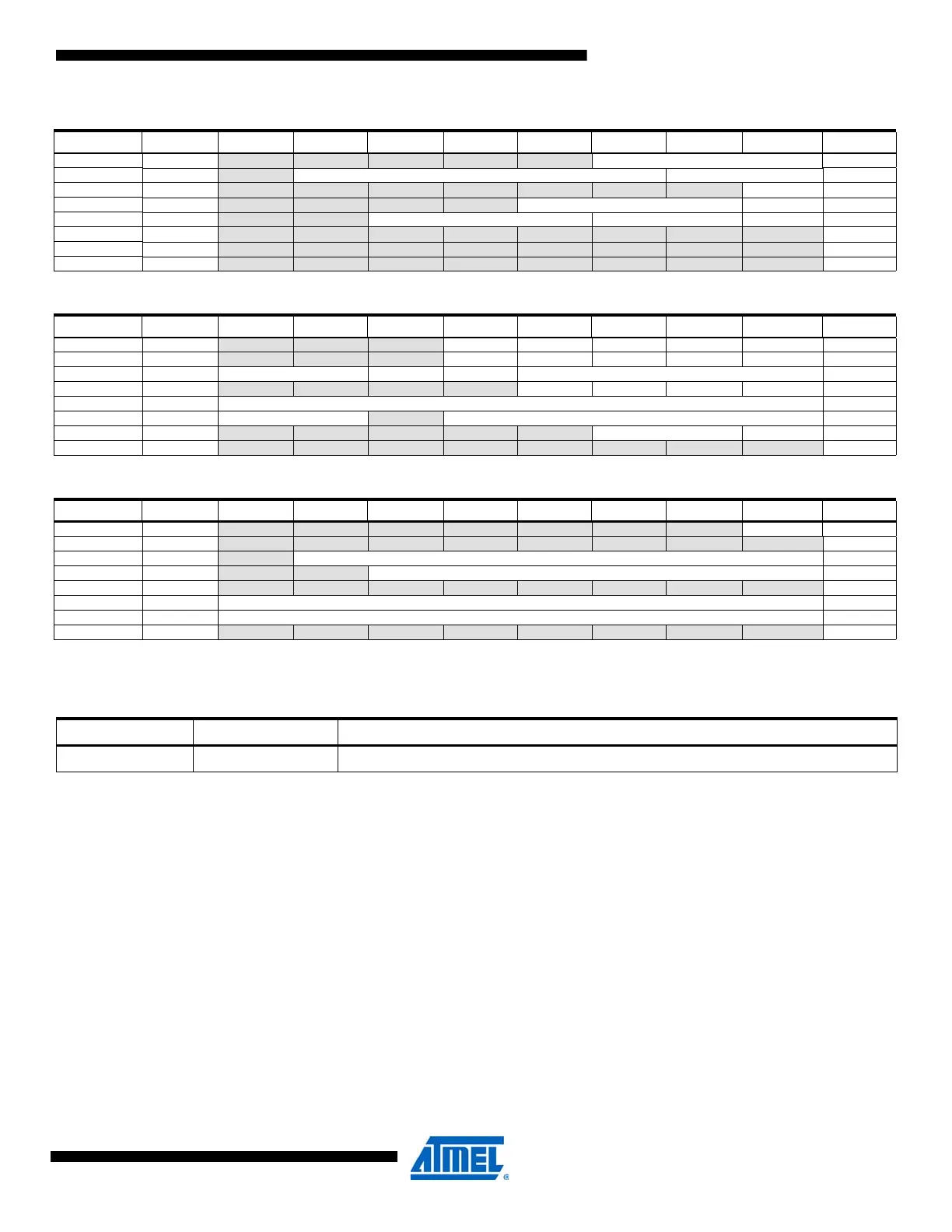

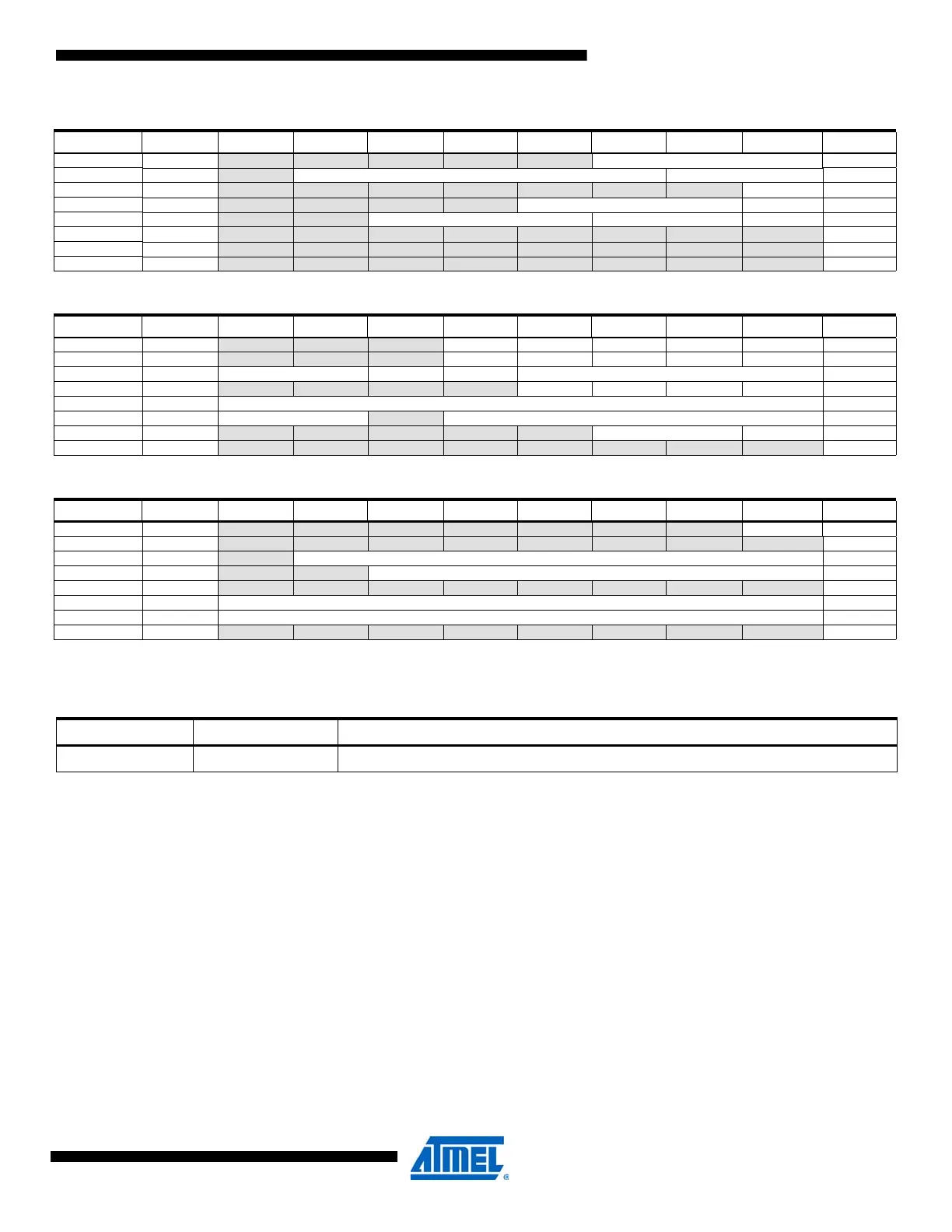

7.12 Register Summary - Clock

7.13 Register Summary - Oscillator

7.14 Register Summary - DFLL32M/DFLL2M

7.15 Oscillator Failure Interrupt Vector Summary

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

+0x00 CTRL – – – – – SCLKSEL[2:0] 92

+0x01 PSCTRL – PSADIV[4:0] PSBCDIV[1:0] 92

+0x02 LOCK – – – – – – –LOCK94

+0x03 RTCCTRL – – – – RTCSRC[2:0] RTCEN 94

+0x04 USBSCTRL – – USBPSDIV[2:0] USBSRC[1:0] USBSEN 94

+0x05 Reserved – – – – – – – –

+0x06 Reserved – – – – – – – –

+0x07 Reserved – – – – – – – –

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

+0x00 CTRL – – – PLLEN XOSCEN RC32KEN R32MEN RC2MEN 96

+0x01 STATUS – – – PLLRDY XOSCRDY RC32KRDY R32MRDY RC2MRDY 96

+0x02 XOSCCTRL FRQRANGE[1:0] X32KLPM XOSCPWR XOSCSEL[3:0] 97

+0x03 XOSCFAIL – – – – PLLFDIF PLLFDEN XOSCFDIF XOSCFDEN 99

+0x04 RC32KCAL RC32KCAL[7:0] 99

+0x05 PLLCTRL PLLSRC[1:0]

– PLLFAC[4:0] 100

+0x06 DFLLCTRL

– – – – – RC32MCREF[1:0] RC2MCREF 100

+0x07 Reserved – – – – – – – –

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

+0x00 CTRL – – – – – – –ENABLE101

+0x01 Reserved – – – – – – – –

+0x02 CALA – CALA[6:0] 101

+0x03 CALB – – CALB[5:0] 102

+0x04 Reserved – – – – – – – –

+0x05 COMP1 COMP[7:0] 102

+0x06 COMP2 COMP[15:8] 103

+0x07 Reserved – – – – – – – –

Table 7-12. Oscillator failure interrupt vector and its word offset address PLL and external oscillator failure interrupt base.

Offset Source Interrupt Description

0x00 OSCF_vect PLL and external oscillator failure interrupt vector (NMI)

Loading...

Loading...