99

8331B–AVR–03/12

Atmel AVR XMEGA AU

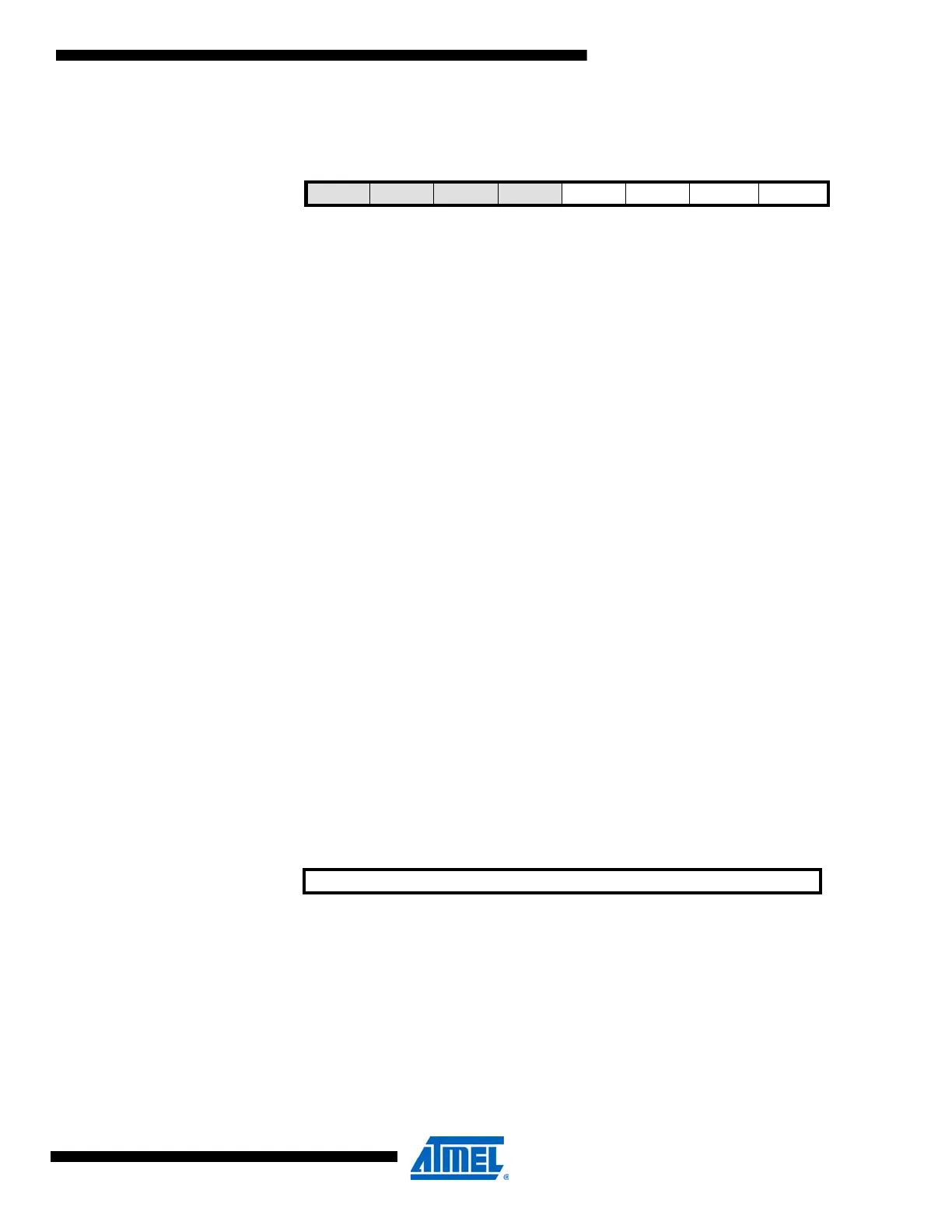

7.10.4 XOSCFAIL – XOSC Failure Detection register

• Bit 7:4 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 3 – PLLFDIF: PLL Fault Detection Flag

If PLL failure detection is enabled, PLLFDIF is set when the PLL looses lock. Writing logic one to

this location will clear PLLFDIF.

• Bit 2 – PLLFDEN: PLL Fault Detection Enable

Setting this bit will enable PLL failure detection. A non-maskable interrupt will be issued when

PLLFDIF is set.

This bit is protected by the configuration change protection mechanism. Refer to ”Configuration

Change Protection” on page 13 for details.

• Bit 1 – XOSCFDIF: Failure Detection Interrupt Flag

If the external clock source oscillator failure monitor is enabled, XOSCFDIF is set when a failure

is detected. Writing logic one to this location will clear XOSCFDIF.

• Bit 0 – XOSCFDEN: Failure Detection Enable

Setting this bit will enable the failure detection monitor, and a non-maskable interrupt will be

issued when XOSCFDIF is set.

This bit is protected by the configuration change protection mechanism. Refer to ”Configuration

Change Protection” on page 13 for details. Once enabled, failure detection can only be disabled

by a reset.

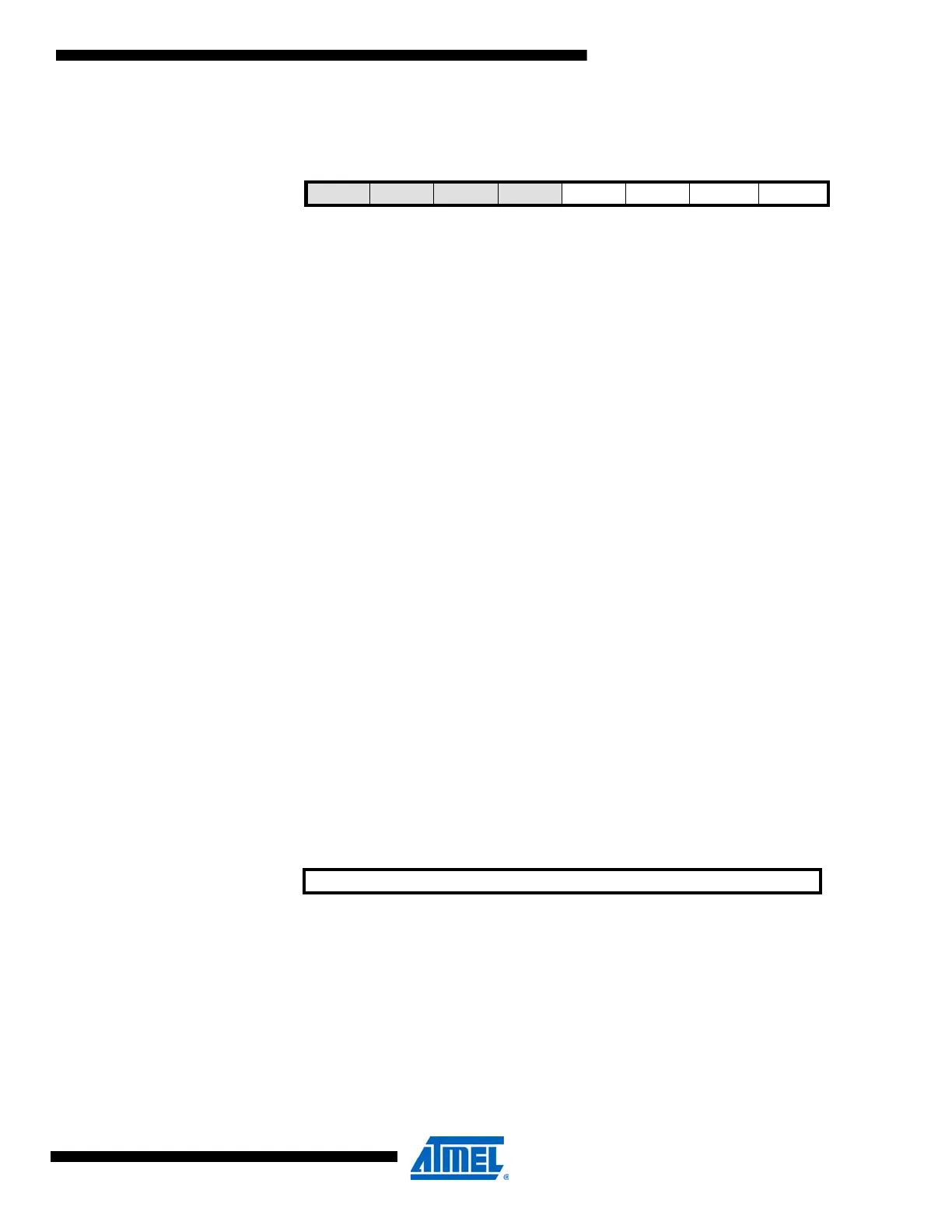

7.10.5 RC32KCAL – 32kHz Oscillator Calibration register

• Bit 7:0 – RC32KCAL[7:0]: 32.768kHz Internal Oscillator Calibration Register

This register is used to calibrate the 32.768kHz internal oscillator. A factory-calibrated value is

loaded from the signature row of the device and written to this register during reset, giving an

oscillator frequency close to 32.768kHz. The register can also be written from software to cali-

brate the oscillator frequency during normal operation.

Bit 765432 1 0

+0x03 – – – – PLLFDIF PLLFDEN XOSCFDIF XOSCFDEN XOSCFAIL

Read/Write R R R R R/W R/W R/W R/W

Initial Value000000 0 0

Bit 76543210

+0x04 RC32KCAL[7:0] RC32KCAL

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Valuexxxxxxxx

Loading...

Loading...