96

8331B–AVR–03/12

Atmel AVR XMEGA AU

7.10 Register Description – Oscillator

7.10.1 CTRL – Oscillator Control register

• Bit 7:5 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 4 – PLLEN: PLL Enable

Setting this bit enables the PLL. Before the PLL is enabled, it must be configured with the

desired multiplication factor and clock source. See ”STATUS – Oscillator Status register” on

page 97.

• Bit 3 – XOSCEN: External Oscillator Enable

Setting this bit enables the selected external clock source. Refer to ”XOSCCTRL – XOSC Con-

trol register” on page 97 for details on how to select the external clock source. The external clock

source should be allowed time to stabilize before it is selected as the source for the system

clock. See ”STATUS – Oscillator Status register” on page 97.

• Bit 2 – RC32KEN: 32.768kHz Internal Oscillator Enable

Setting this bit enables the 32.768kHz internal oscillator. The oscillator must be stable before it

is selected as the source for the system clock. See ”STATUS – Oscillator Status register” on

page 97.

• Bit 1 – RC32MEN: 32MHz Internal Oscillator Enable

Setting this bit will enable the 32MHz internal oscillator. The oscillator must be stable before it is

selected as the source for the system clock. See ”STATUS – Oscillator Status register” on page

97.

• Bit 0 – RC2MEN: 2MHz Internal Oscillator Enable

Setting this bit enables the 2MHz internal oscillator. The oscillator must be stable before it is

selected as the source for the system clock. See ”STATUS – Oscillator Status register” on page

97.

By default, the 2MHz internal oscillator is enabled and this bit is set.

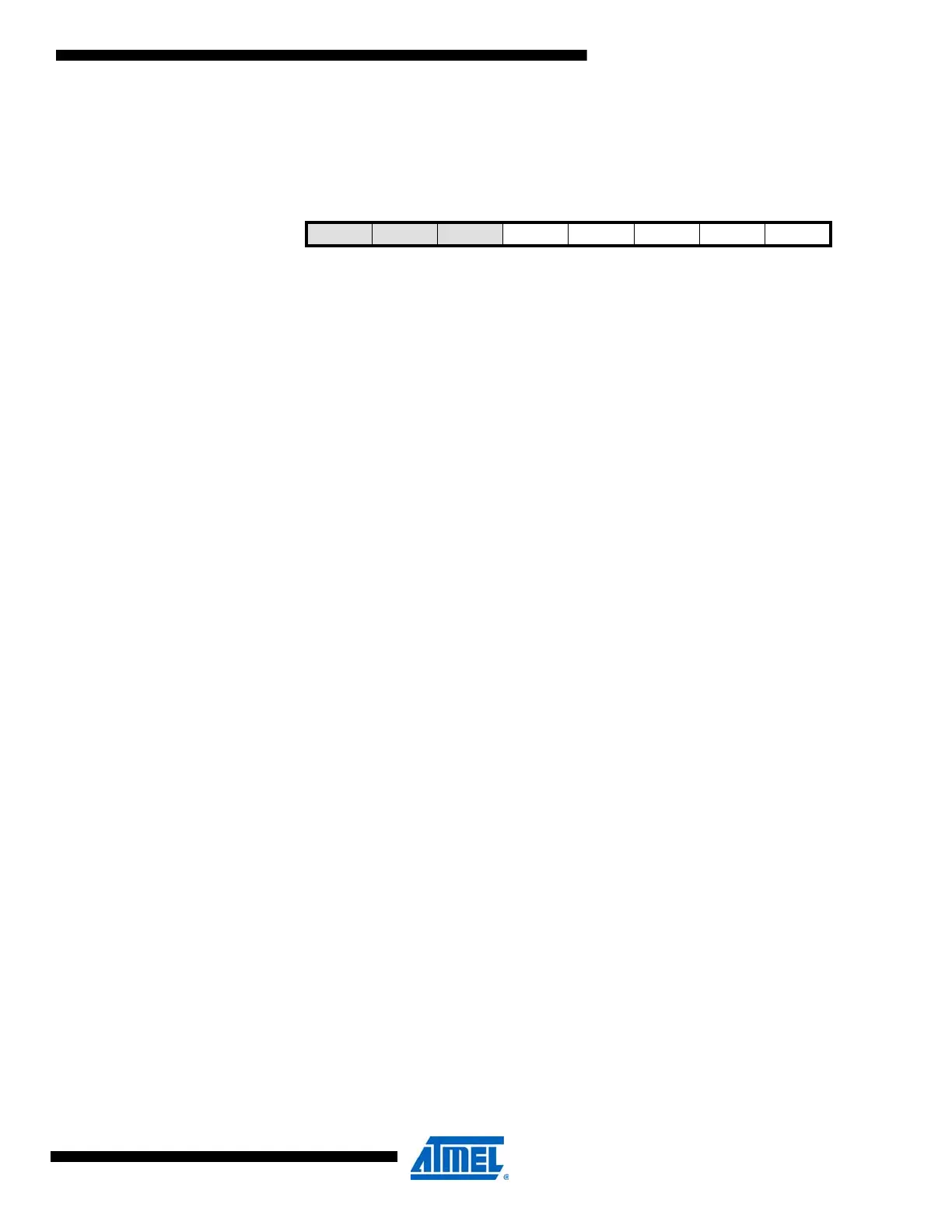

Bit 76543210

+0x00 – – – PLLEN XOSCEN RC32KEN RC32MEN RC2MEN CTRL

Read/Write R R R R/W R/W R/W R/W R/W

Initial Value00000001

Loading...

Loading...