59

8331B–AVR–03/12

Atmel AVR XMEGA AU

5.13 Register Description – DMA Controller

5.13.1 CTRL – Control register

• Bit 7 – ENABLE: Enable

Setting this bit enables the DMA controller. If the DMA controller is enabled and this bit is written

to zero, the ENABLE bit is not cleared before the internal transfer buffer is empty, and the DMA

data transfer is aborted.

• Bit 6 – RESET: Software Reset

Writing a one to RESET will be ignored as long as DMA is enabled (ENABLE = 1). This bit can

be set only when the DMA controller is disabled (ENABLE = 0).

• Bit 5:4 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 3:2 – DBUFMODE[1:0]: Double Buffer Mode

These bits enable the double buffer on the different channels according to Table 5-1.

• Bit 1:0 – PRIMODE[1:0]: Channel Priority Mode

These bits determine the internal channel priority according to Table 5-2.

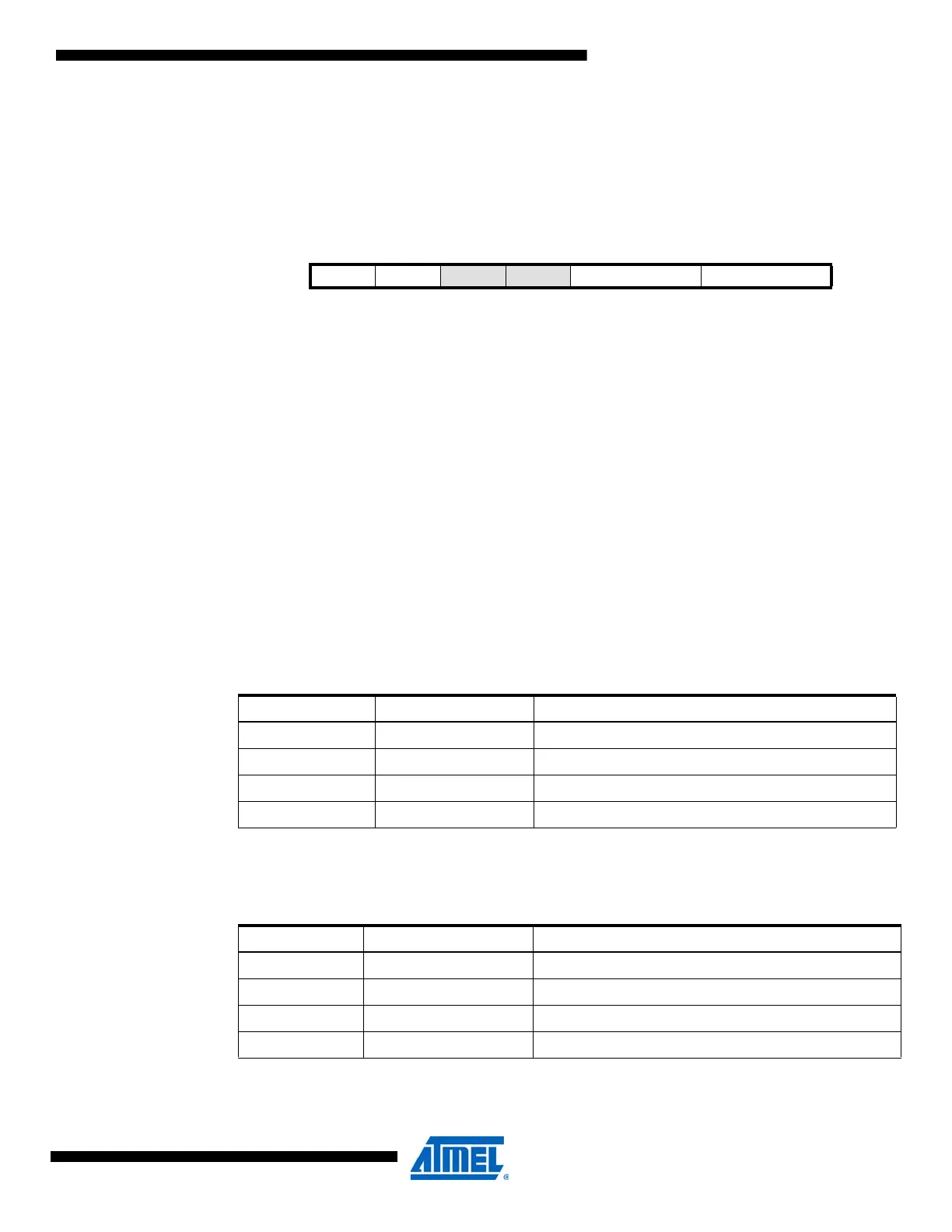

Bit 76543210

+0x00 ENABLE RESET – – DBUFMODE[1:0] PRIMODE[1:0] CTRL

Read/Write R/W R/W R R R/W R/W R/W R/W

Initial Value00000000

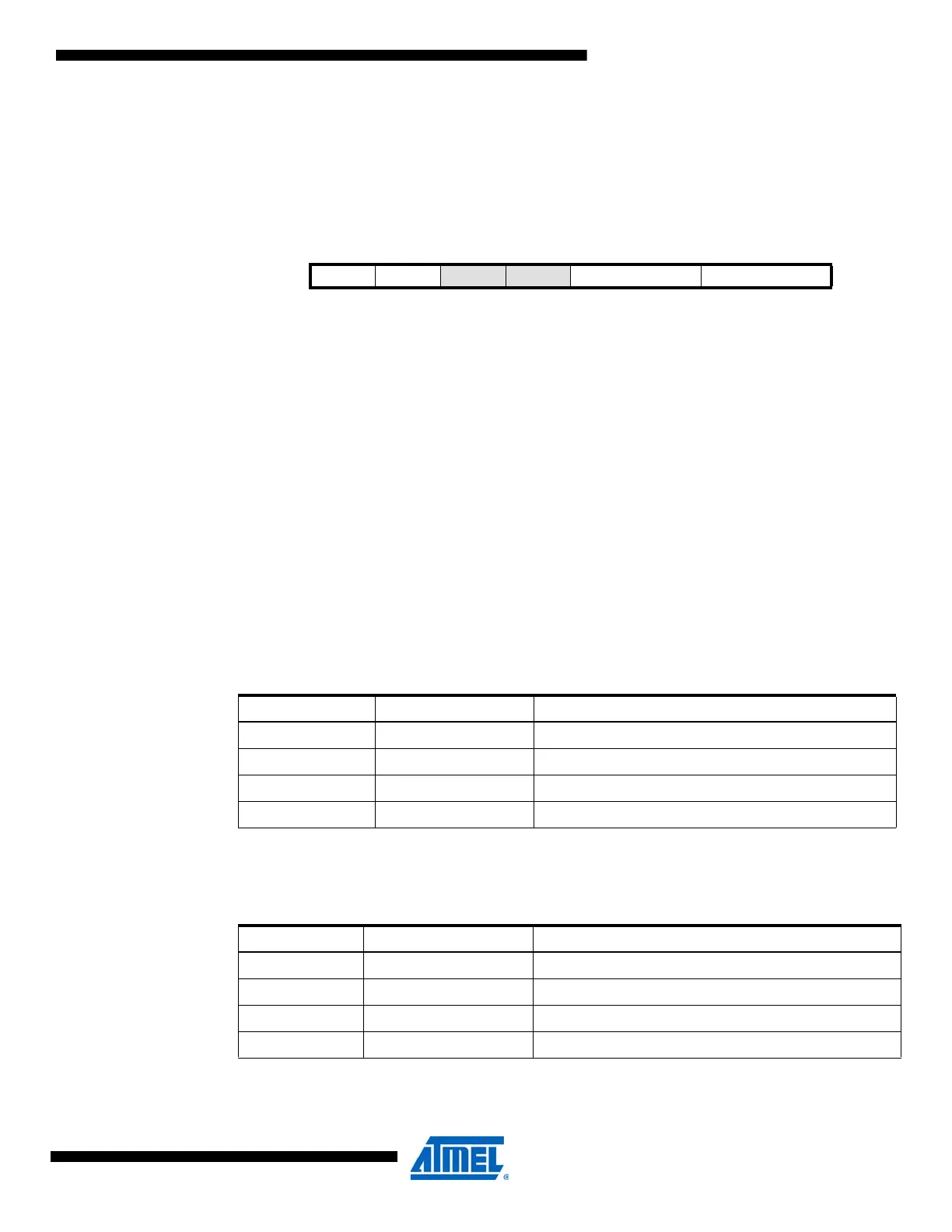

Table 5-1. DMA double buffer settings.

DBUFMODE[1:0] Group Configuration Description

00 DISABLED No double buffer enabled

01 CH01 Double buffer enabled on channel0/1

10 CH23 Double buffer enabled on channel2/3

11 CH01CH23 Double buffer enabled on channel0/1 and channel2/3

Table 5-2. DMA channel priority settings.

PRIMODE[1:0] Group Configuration Description

00 RR0123 Round robin

01 CH0RR123 Channel0 > Round robin (channel 1, 2 and 3)

10 CH01RR23 Channel0 > Channel1 > Round robin (channel 2 and 3)

11 CH0123 Channel0 > Channel1 > Channel2 > Channel3

Loading...

Loading...