218

8331B–AVR–03/12

Atmel AVR XMEGA AU

The hi-res extension will not output any pulse shorter than one peripheral clock cycle; i.e., a

compare value lower than four will have no visible output.

17.3 Register Description

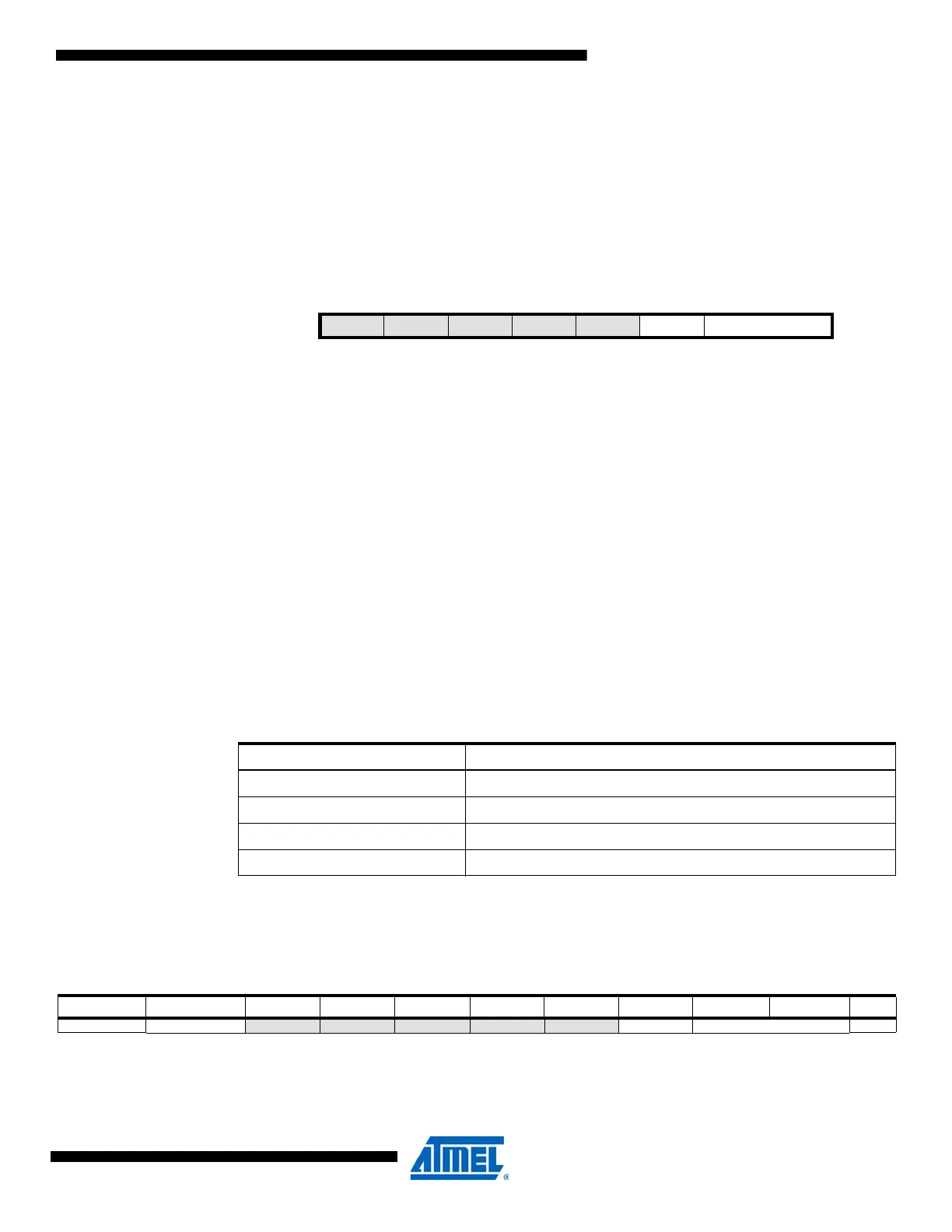

17.3.1 CTRLA – Control register A

• Bit 7:3 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 2 – HRPLUS: High Resolution Plus

Setting this bit enables high resolution plus. Hi-res plus is the same as hi-res, but will increase

the resolution by eight (3 bits) instead of four.

The extra resolution is achieved by operating at both edges of the peripheral 4x clock.

• Bit 1:0 – HREN[1:0]: High Resolution Enable

These bits enables the high-resolution mode for a timer/counter according to Table 17-1.

Setting one or both HREN bits will enable high-resolution waveform generation output for the

entire general purpose I/O port. This means that both timer/counters connected to the same port

must enable hi-res if both are used for generating PWM or FRQ output on pins.

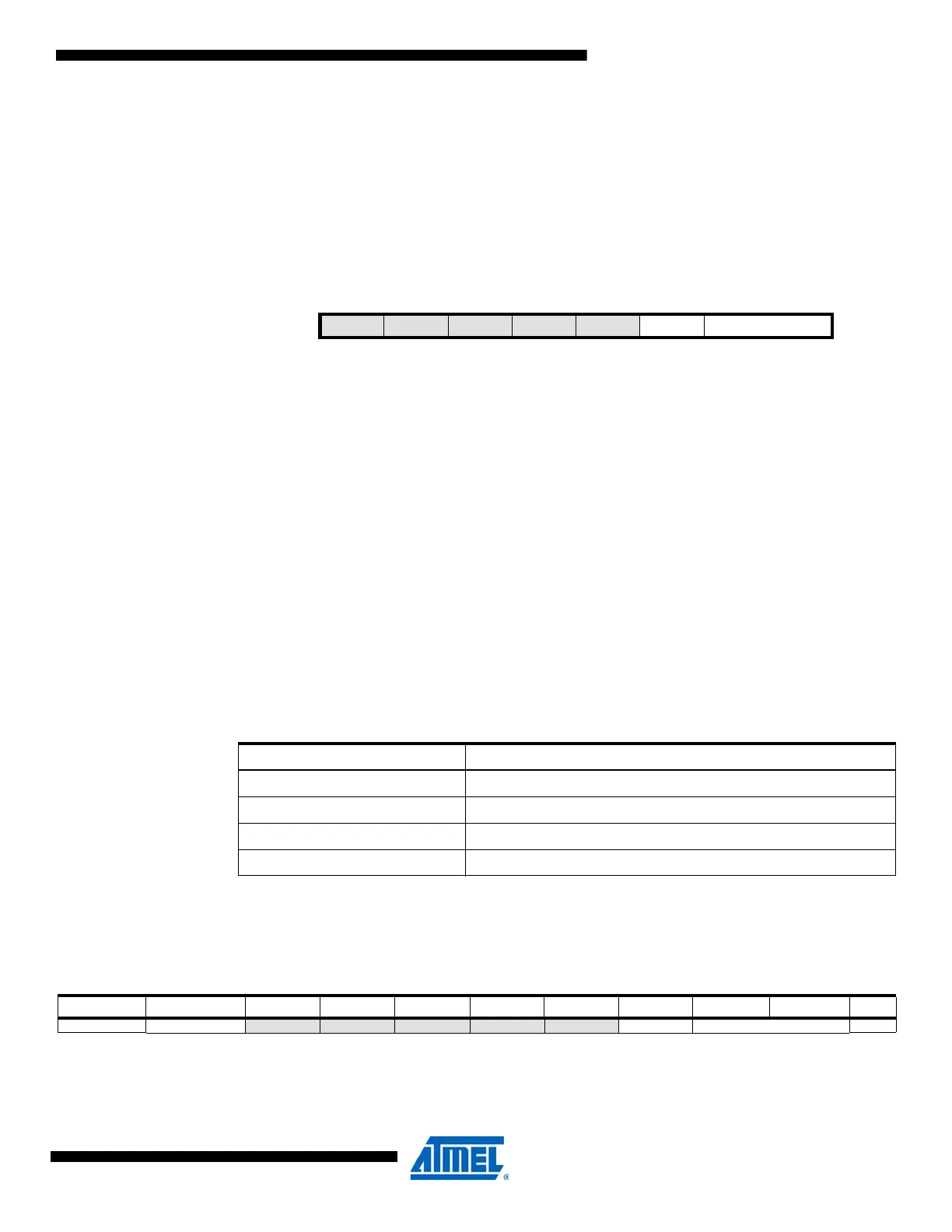

17.4 Register Summary

Bit 76543210

+0x00 – – – – – HRPLUS HREN[1:0] CTRLA

Read/Write R R R R R R/W R/W R/W

Initial Value00000000

Table 17-1. High Resolution Enable

HREN[1:0] High Resolution Enabled

00 None

01 Timer/counter 0

10 Timer/counter 1

11 Both timer/counters

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

+0x00 CTRLA – – – – – HRPLUS HREN[1:0] 218

Loading...

Loading...