92

8331B–AVR–03/12

Atmel AVR XMEGA AU

7.9 Register Description – Clock

7.9.1 CTRL – Control register

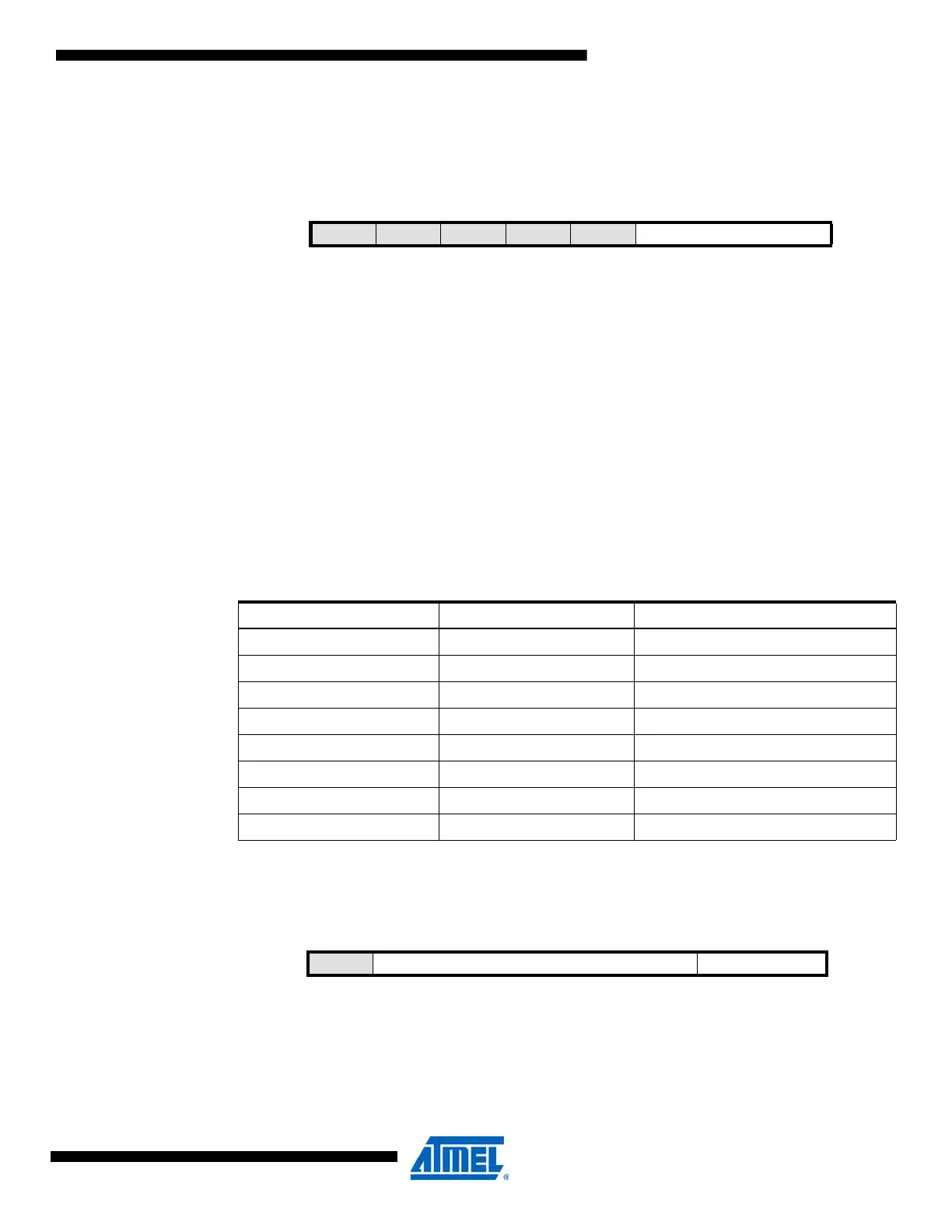

• Bit 7:3 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 2:0 – SCLKSEL[2:0]: System Clock Selection

These bits are used to select the source for the system clock. See Table 7-1 for the different

selections. Changing the system clock source will take two clock cycles on the old clock source

and two more clock cycles on the new clock source. These bits are protected by the configura-

tion change protection mechanism. For details, refer to ”Configuration Change Protection” on

page 13.

SCLKSEL cannot be changed if the new clock source is not stable. The old clock can not be dis-

abled until the clock switching is completed.

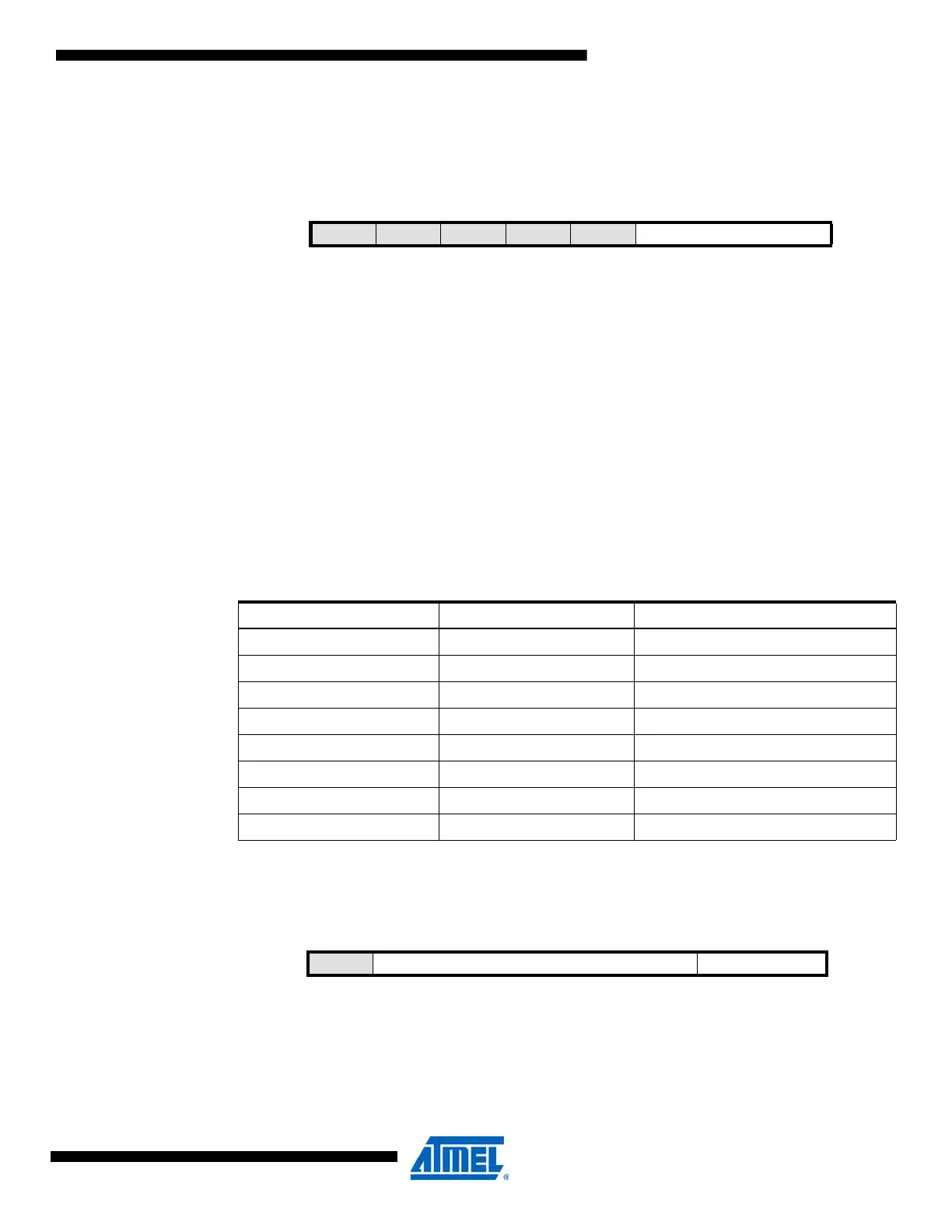

7.9.2 PSCTRL – Prescaler register

This register is protected by the configuration change protection mechanism. For details, refer to

”Configuration Change Protection” on page 13.

• Bit 7 – Reserved

This bit is unused and reserved for future use. For compatibility with future devices, always write

this bit to zero when this register is written.

Bit 76543210

+0x00 – – – – –SCLKSEL[2:0]CTRL

Read/WriteRRRRRR/WR/WR/W

Initial Value00000000

Table 7-1. System clock selection.

SCLKSEL[2:0] Group Configuration Description

000 RC2MHZ 2MHz internal oscillator

001 RC32MHZ 32MHz internal oscillator

010 RC32KHZ 32.768kHz internal oscillator

011 XOSC External oscillator or clock

100 PLL Phase locked loop

101 — Reserved

110 — Reserved

111 — Reserved

Bit 76543210

+0x01 – PSADIV[4:0] PSBCDIV PSCTRL

Read/Write R R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

Loading...

Loading...