397

8331B–AVR–03/12

Atmel AVR XMEGA AU

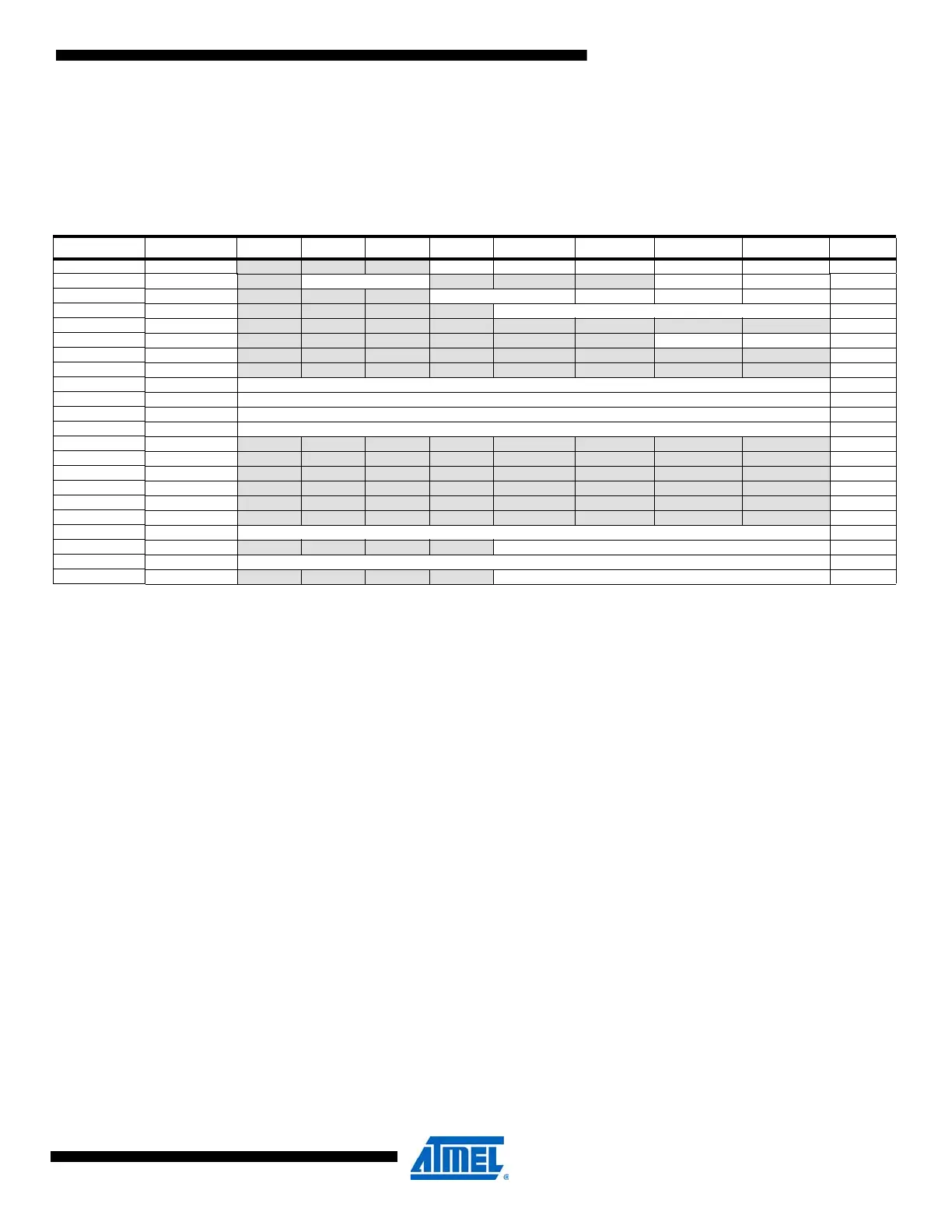

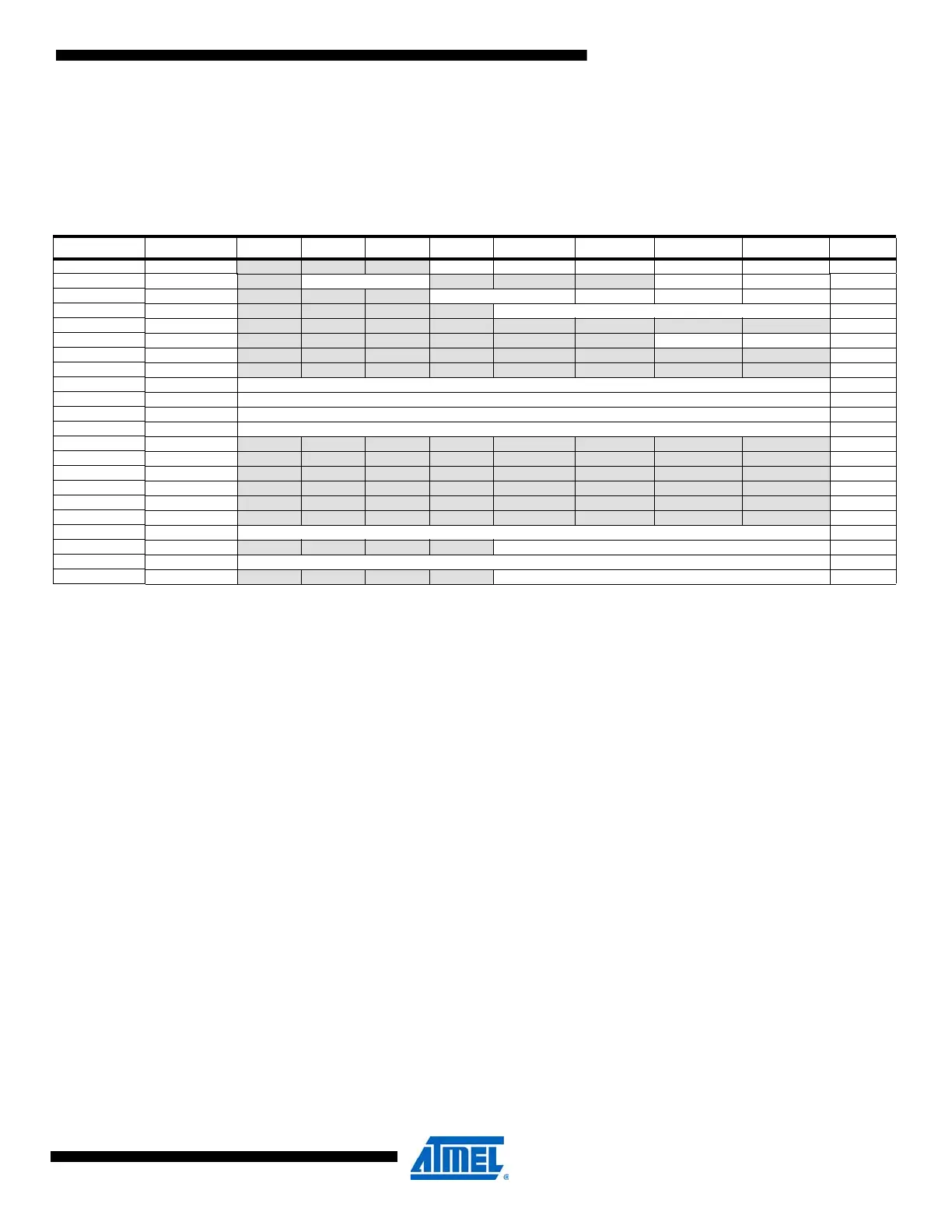

29.11 Register Summary

This is the I/O summary when the DAC is configured to give standard 12-bit results. The I/O

summary for 12-bit left-adjusted results will be similar, but with some changes in the CHnDATAL

and CHnDATAH data registers.

Address Name Bit 7 Bit 6 Bit 5 Bit 4 Bit 3 Bit 2 Bit 1 Bit 0 Page

+0x00 CTRLA – – – IDOEN CH1EN CH0EN LPMODE ENABLE 390

+0x01 CTRLB – CHSEL[1:0] – – – CH1TRIG CH0TRIG 390

+0x02 CTRLC – – – REFSEL[1:0] - - LEFTADJ 391

+0x03 EVCTRL – – – – EVSEL[3:0] 392

+0x04 Reserved – – – – – – – –

+0x05 STATUS – – – – – – CH1DRE CH0DRE 392

+0x06 Reserved – – – – – – – –

+0x07 Reserved – – – – – – – –

+0x08 CH0GAINCAL CH0GAINCAL[7:0] 395

+0x09 CH0OFFSETCAL CH0OFFSETCAL[7:0] 395

+0x0A CH0GAINCAL CH1GAINCAL[7:0]

+0x0B CH0OFFSETCAL CH1OFFSETCAL[7:0]

+0x12 Reserved – – – – – – – –

+0x13 Reserved – – – – – – – –

+0x14 Reserved – – – – – – – –

+0x15 Reserved – – – – – – – –

+0x16 Reserved – – – – – – – –

+0x17 Reserved – – – – – – – –

+0x18 CH0DATAL CHDATA[7:0] 394

+0x19 CH0DATAH – – – – CHDATA[11:8] 393

+0x1A CH1DATAL CHDATA[7:0] 395

+0x1B CH1DATAH – – – – CHDATA[11:8] 394

Loading...

Loading...