392

8331B–AVR–03/12

Atmel AVR XMEGA AU

• Bit 0 - LEFTADJ: Left-Adjust Value

If this bit is set, CH0DATA and CH1DATA are left-adjusted.

29.10.4 EVCTRL – Event Control Register

• Bit 7:4 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 3 – EVSEL[3]: Event Selection bit 3

Setting this bit to 1 enables event channel EVSEL[2:0]+1 as the trigger source for DAC Channel

1. When this bit is 0, the same event channel is used as the trigger source for both DAC

channels.

• Bit 2:0 – EVSEL[2:0]: Event Channel Input Selection

These bits select which Event System channel is used for triggering a DAC conversion. Table

29-3 shows the available selections.

29.10.5 STATUS – Status Register

• Bit 7:2 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

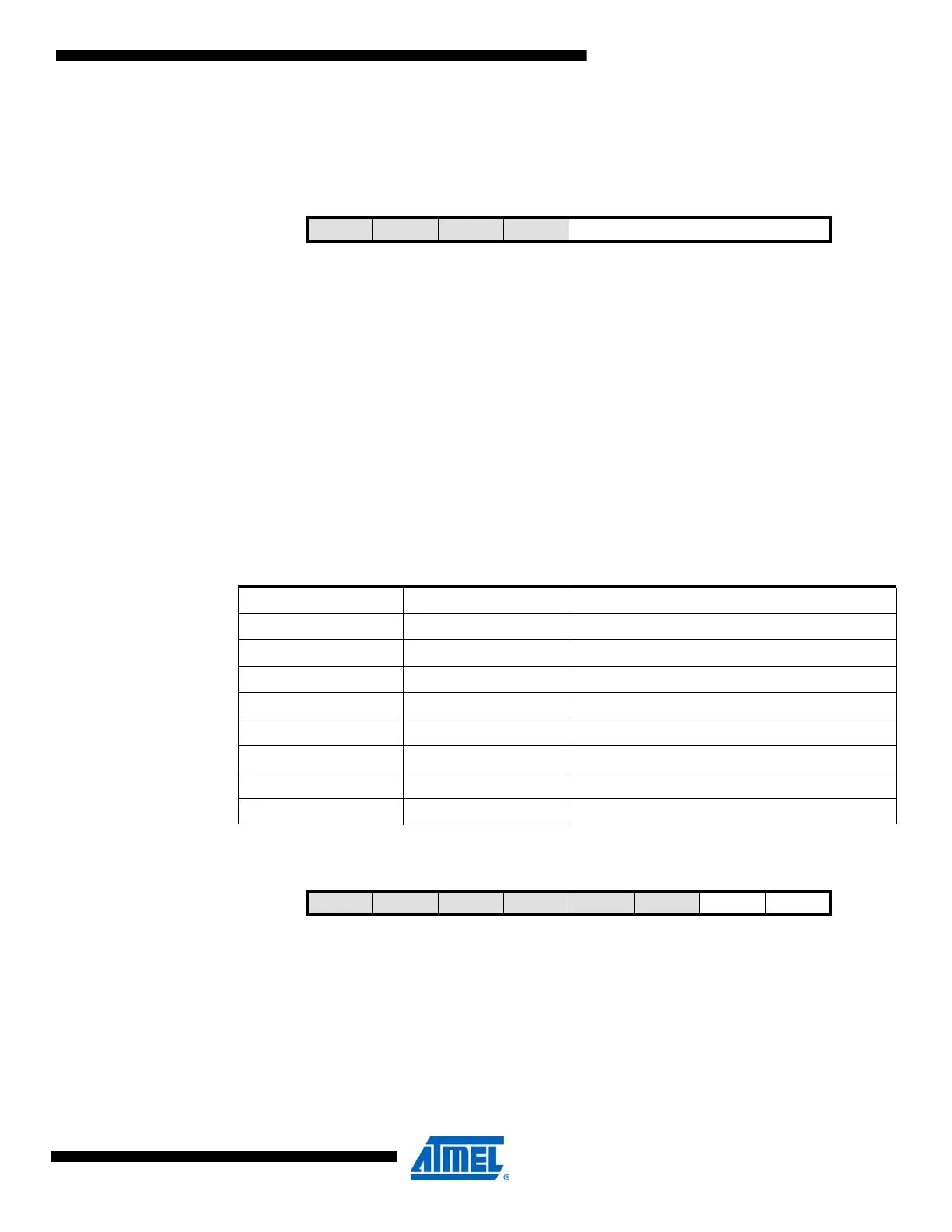

Bit 76543210

+0x03 – – – – EVSEL[3:0] EVCTRL

Read/Write R R R R R/W R/W R/W R/W

Initial Value 0 0 0 0 0 0 0 0

Table 29-3. DAC Event input Selection.

EVSEL[2:0] Group Configuration Description

000 0 Event channel 0 as input to DAC

001 1 Event channel 1 as input to DAC

010 2 Event channel 2 as input to DAC

011 3 Event channel 3 as input to DAC

100 4 Event channel 4 as input to DAC

101 5 Event channel 5 as input to DAC

110 6 Event channel 6 as input to DAC

111 7 Event channel 7 as input to DAC

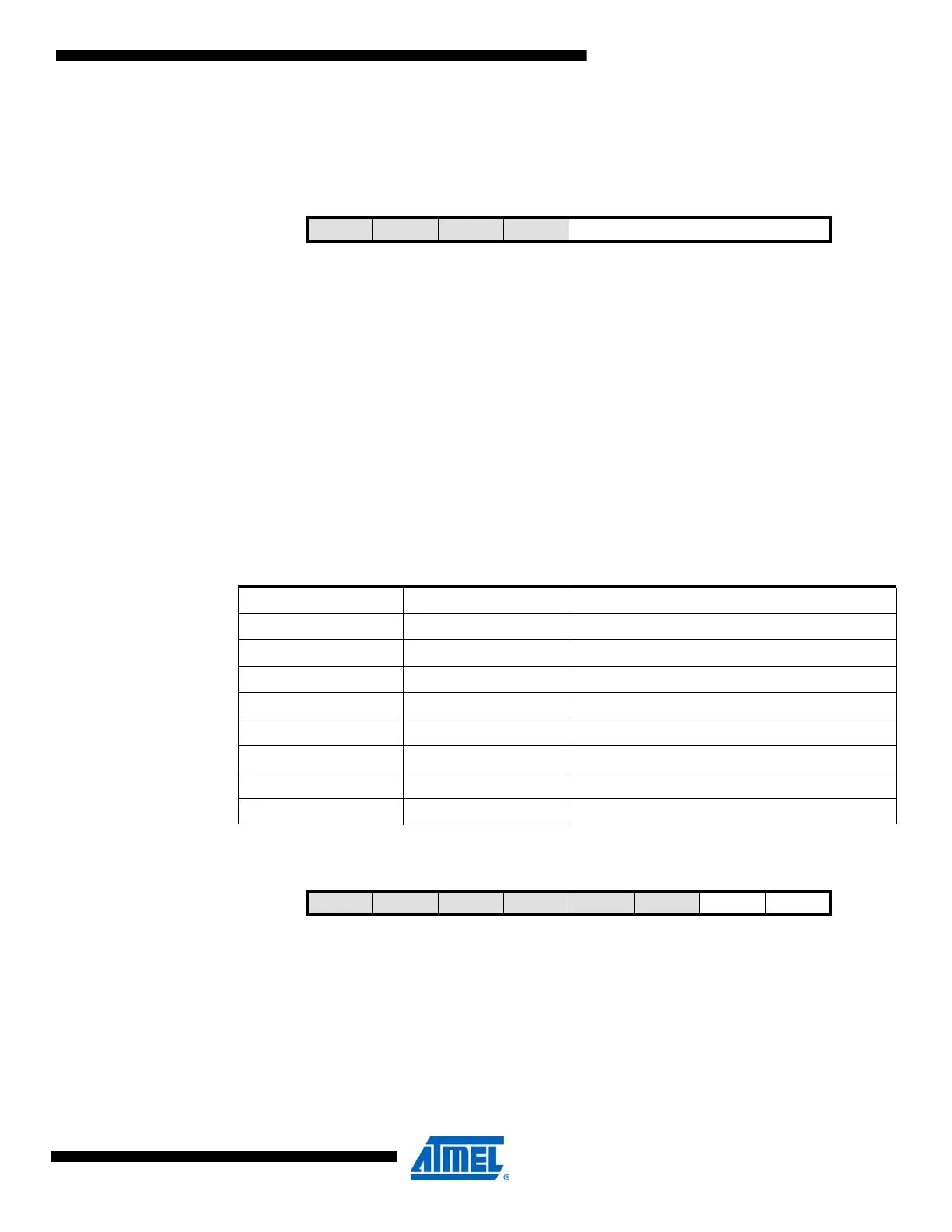

Bit 76543210

+0x05 – – – – – – CH1DRE CH0DRE STATUS

Read/WriteRRRRRRR/WR/W

Initial Value 0 0 0 0 0 0 0 0

Loading...

Loading...