119

8331B–AVR–03/12

Atmel AVR XMEGA AU

9.5 Register Description

9.5.1 STATUS – Status register

• Bit 7:6 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 5 – SRF: Software Reset Flag

This flag is set if a software reset occurs. The flag will be cleared by a power-on reset or by writ-

ing a one to the bit location.

• Bit 4 – PDIRF: Program and Debug Interface Reset Flag

This flag is set if a programming interface reset occurs. The flag will be cleared by a power-on

reset or by writing a one to the bit location.

• Bit 3 – WDRF: Watchdog Reset Flag

This flag is set if a watchdog reset occurs. The flag will be cleared by a power-on reset or by writ-

ing a one to the bit location.

• Bit 2 – BORF: Brownout Reset Flag

This flag is set if a brownout reset occurs. The flag will be cleared by a power-on reset or by writ-

ing a one to the bit location.

• Bit 1 – EXTRF: External Reset Flag

This flag is set if an external reset occurs. The flag will be cleared by a power-on reset or by writ-

ing a one to the bit location.

• Bit 0 – PORF: Power On Reset Flag

This flag is set if a power-on reset occurs. Writing a one to the flag will clear the bit location.

9.5.2 CTRL – Control register

• Bit 7:1 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 0 – SWRST: Software Reset

When this bit is set, a software reset will occur. The bit is cleared when a reset is issued. This bit

is protected by the configuration change protection mechanism. For details, refer to ”Configura-

tion Change Protection” on page 13.

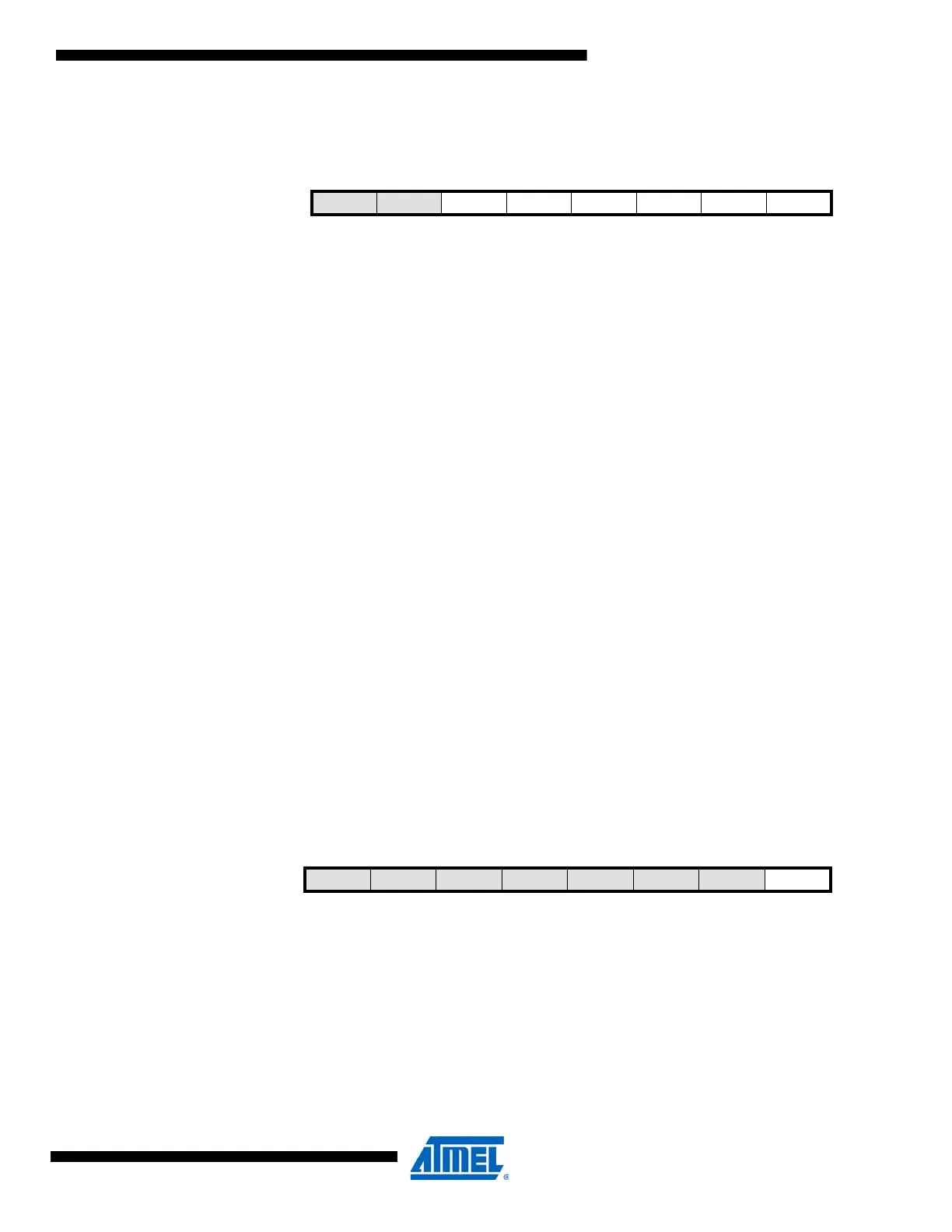

Bit 76543210

+0x00 – – SRF PDIRF WDRF BORF EXTRF PORF STATUS

Read/Write R R R/W R/W R/W R/W R/W R/W

Initial Value--------

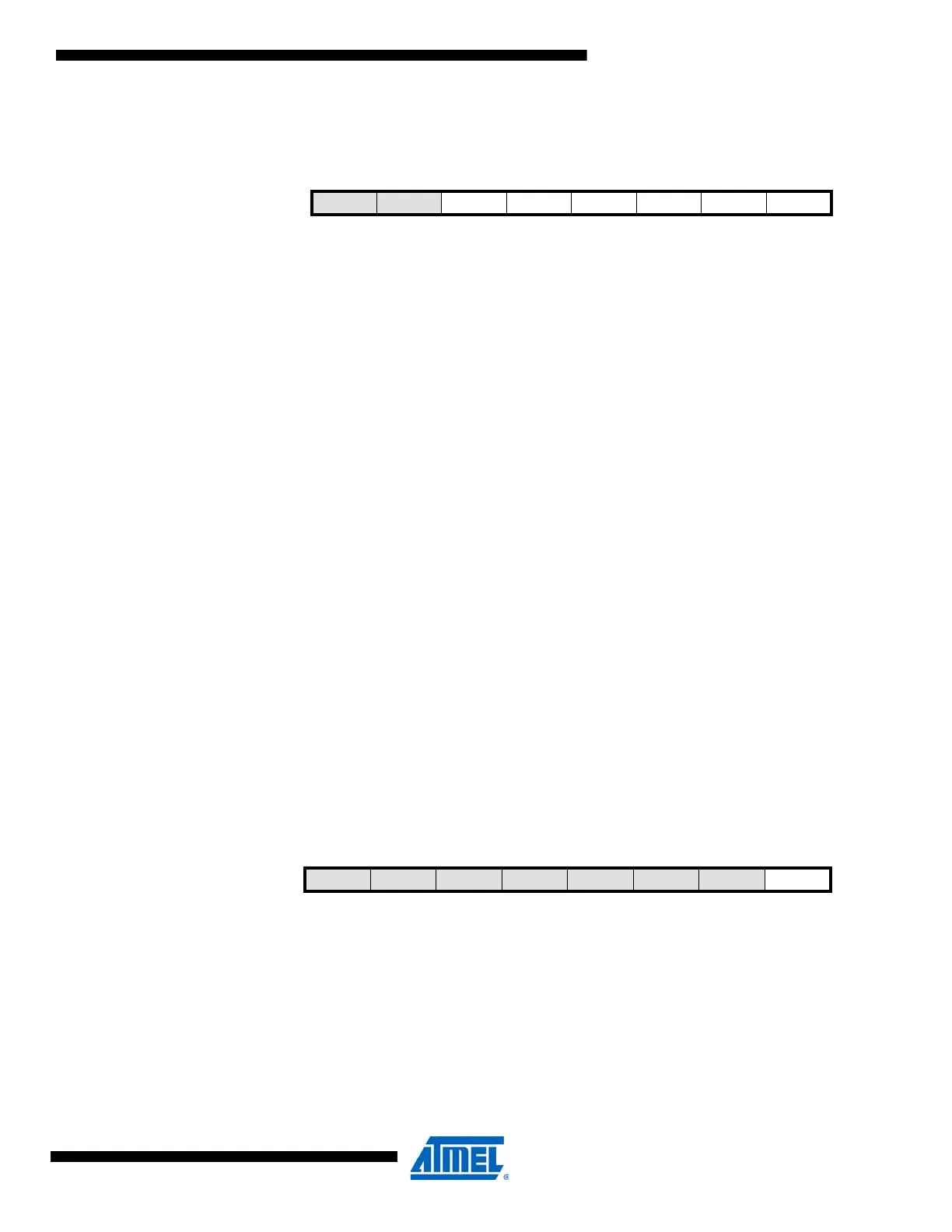

Bit 76543210

+0x01 – – – – – – –SWRSTCTRL

Read/WriteRRRRRRRR/W

Initial Value00000000

Loading...

Loading...