151

8331B–AVR–03/12

Atmel AVR XMEGA AU

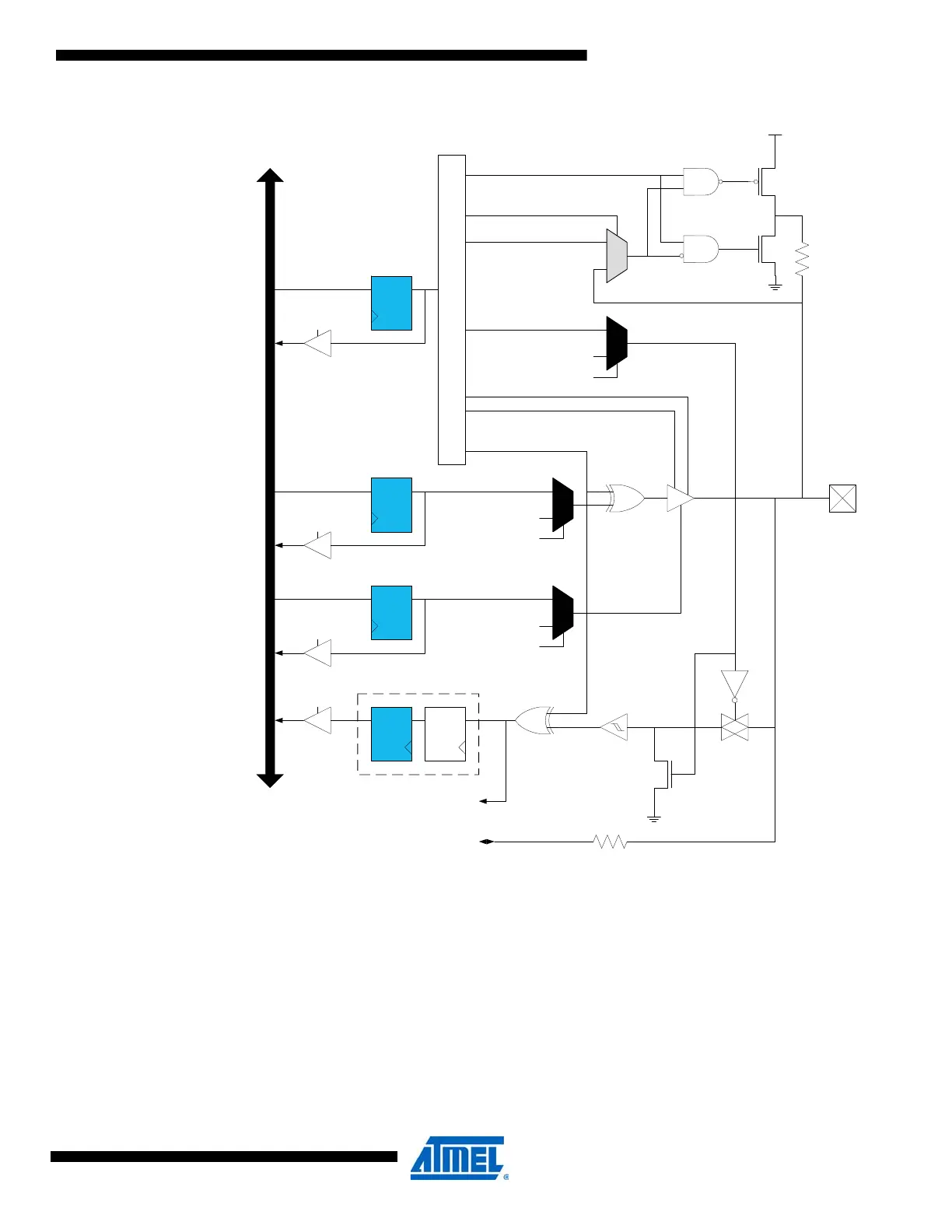

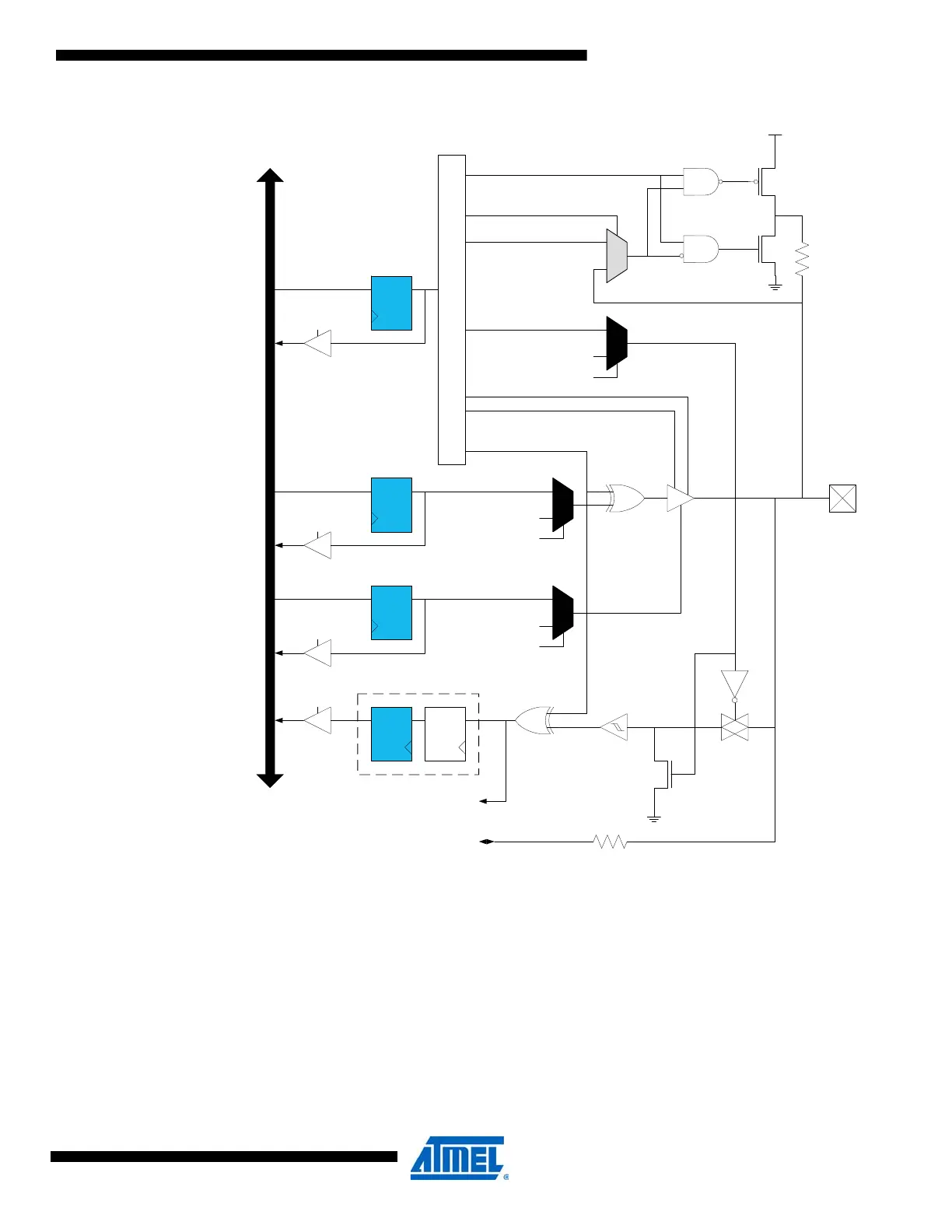

Figure 13-10. Port override signals and related logic.

13.9 Slew Rate Control

Slew rate control can be enabled for all I/O pins individually. Enabling the slew rate limiter will

typically increase the rise/fall time by 50% to 150%, depending on operating conditions and load.

For information about the characteristics of the slew rate limiter, please refer to the device

datasheet.

13.10 Clock and Event Output

It is possible to output the peripheral clock and event channel 0 events to a pin. This can be

used to clock, control, and synchronize external functions and hardware to internal device tim-

ing. The output port pin is selectable. If an event occurs, it remains visible on the port pin as long

as the event lasts; normally one peripheral clock cycle.

D

Q

R

D

Q

R

Synchronizer

D

Q

R

D

Q

R

DIRn

OUTn

PINnCTRL

INn

Pxn

D

Q

R

C

o

n

t

r

o

l

L

o

g

i

c

Digital Input Disable (DID)

Wired AND/OR

Slew Rate Limit

Digital Input Pin

Analog Input/Output

Inverted I/O

Pull Enable

Pull Keep

Pull Direction

DID Override Enable

DID Override Value

OUT Override Enable

OUT Override Value

DIR Override Enable

DIR Override Value

Loading...

Loading...