274

8331B–AVR–03/12

Atmel AVR XMEGA AU

21.8 Register Description – TWI

21.8.1 CTRL – Common Control Register

• Bit 7:3 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 2:1 – SDAHOLD[1:0]: SDA Hold Time Enable.

Setting these bits to one enables an internal hold time on SDA with respect to the negative edge

of SCL.

• Bit 0 – EDIEN: External Driver Interface Enable

Setting this bit enables the use of the external driver interface, and clearing this bit enables nor-

mal two-wire mode. See Table 21-2 on page 274 for details.

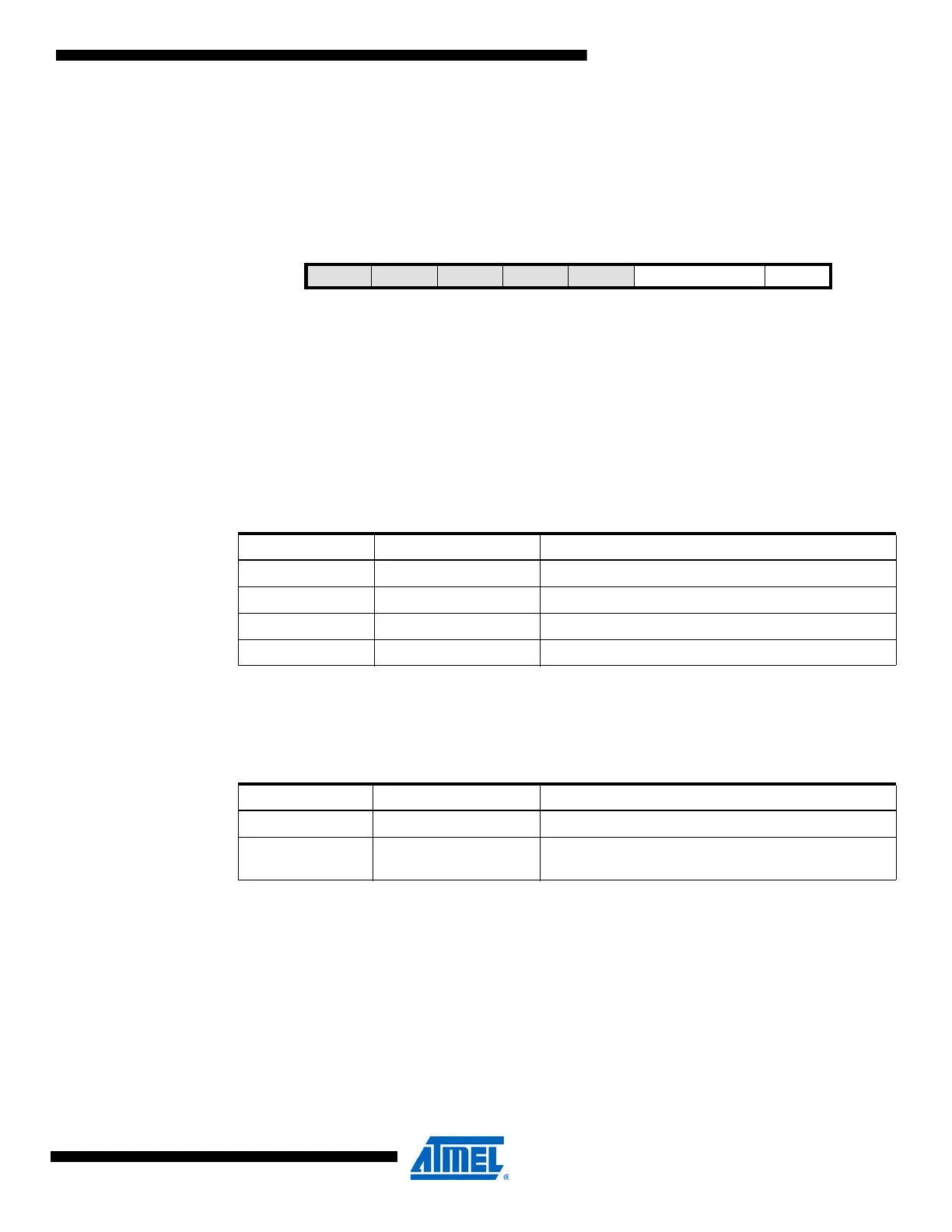

Bit 76543210

+0x00 – – – – – SDAHOLD[1:0] EDIEN CTRL

Read/Write R R R R R R/W R/W R/W

Initial Value00000000

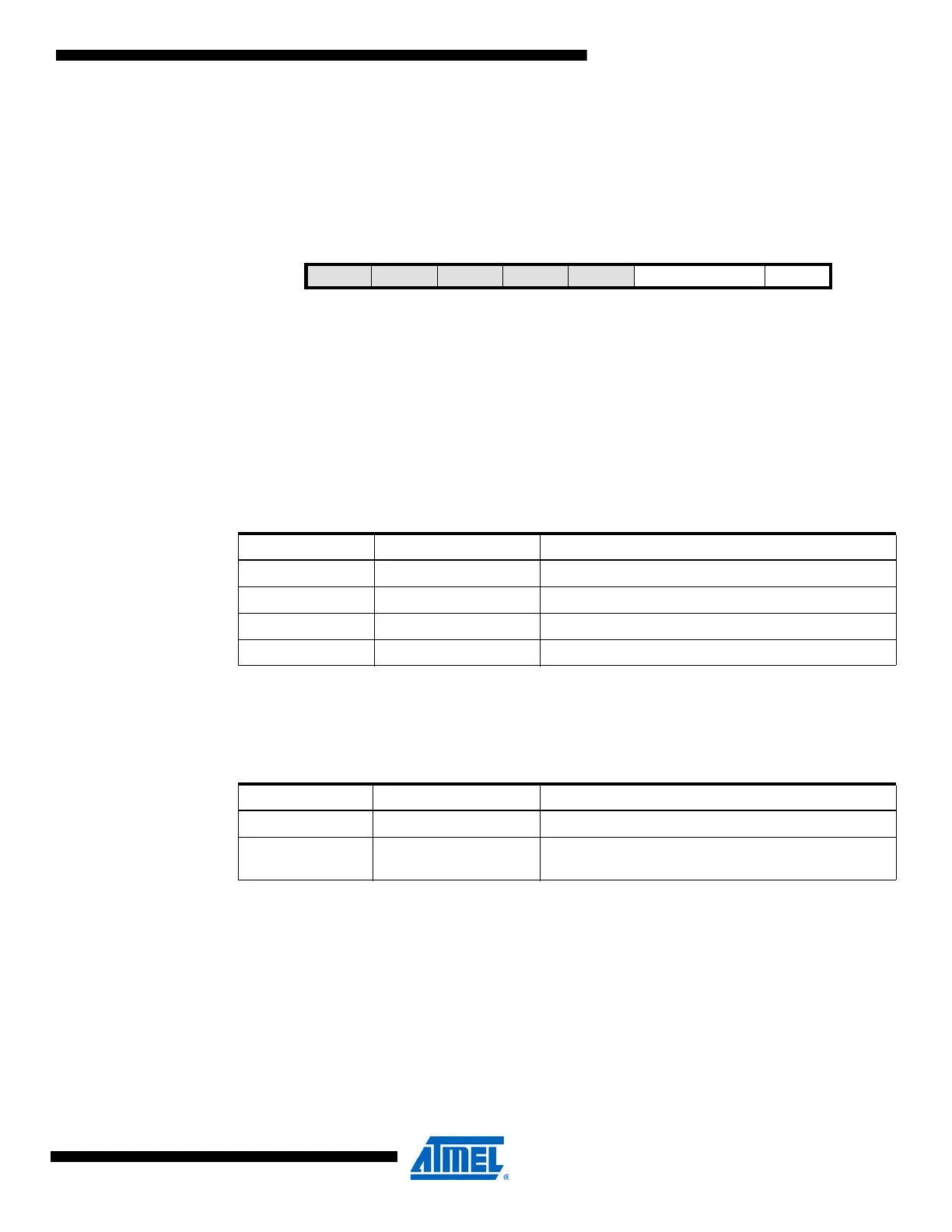

Table 21-1. SDA hold time.

SDAHOLD[1:0] Group Configuration Description

00 OFF SDA hold time off

01 50NS Typical 50ns hold time

10 300NS Typical 100ns hold time

11 400NS Typical 400ns hold time

Table 21-2. External driver interface enable.

EDIEN Mode Comment

0 Normal TWI Two-pin interface,slew rate control, and input filter.

1 External driver interface

Four-pin interface, standard I/O, no slew rate control,

and no input filter.

Loading...

Loading...