97

8331B–AVR–03/12

Atmel AVR XMEGA AU

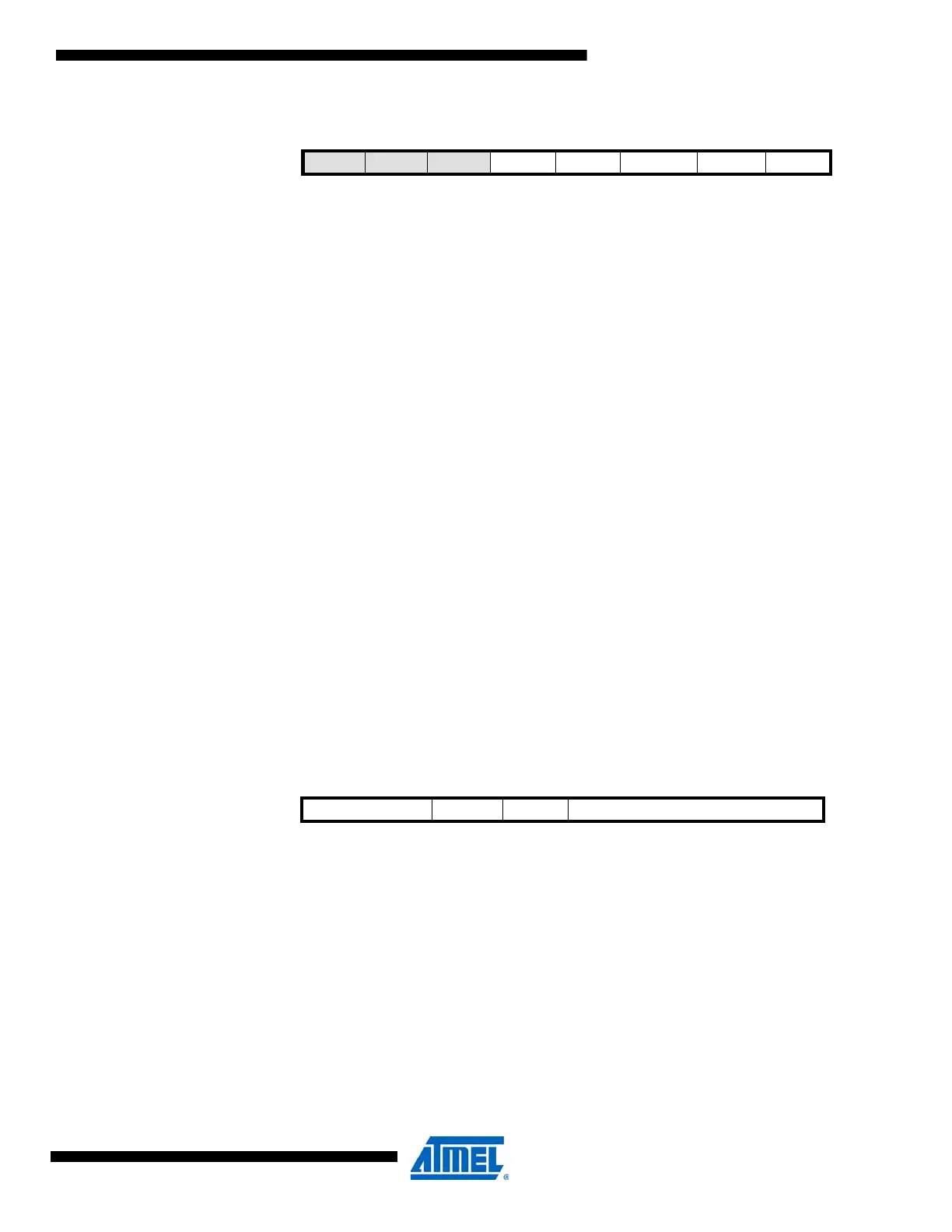

7.10.2 STATUS – Oscillator Status register

• Bit 7:5 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 4 – PLLRDY: PLL Ready

This flag is set when the PLL has locked on the selected frequency and is ready to be used as

the system clock source.

• Bit 3 – XOSCRDY: External Clock Source Ready

This flag is set when the external clock source is stable and is ready to be used as the system

clock source.

• Bit 2 – RC32KRDY: 32.768kHz Internal Oscillator Ready

This flag is set when the 32.768kHz internal oscillator is stable and is ready to be used as the

system clock source.

• Bit 1 – RC32MRDY: 32MHz Internal Oscillator Ready

This flag is set when the 32MHz internal oscillator is stable and is ready to be used as the sys-

tem clock source.

• Bit 0 – RC2MRDY: 2MHz Internal Oscillator Ready

This flag is set when the 2MHz internal oscillator is stable and is ready to be used as the system

clock source.

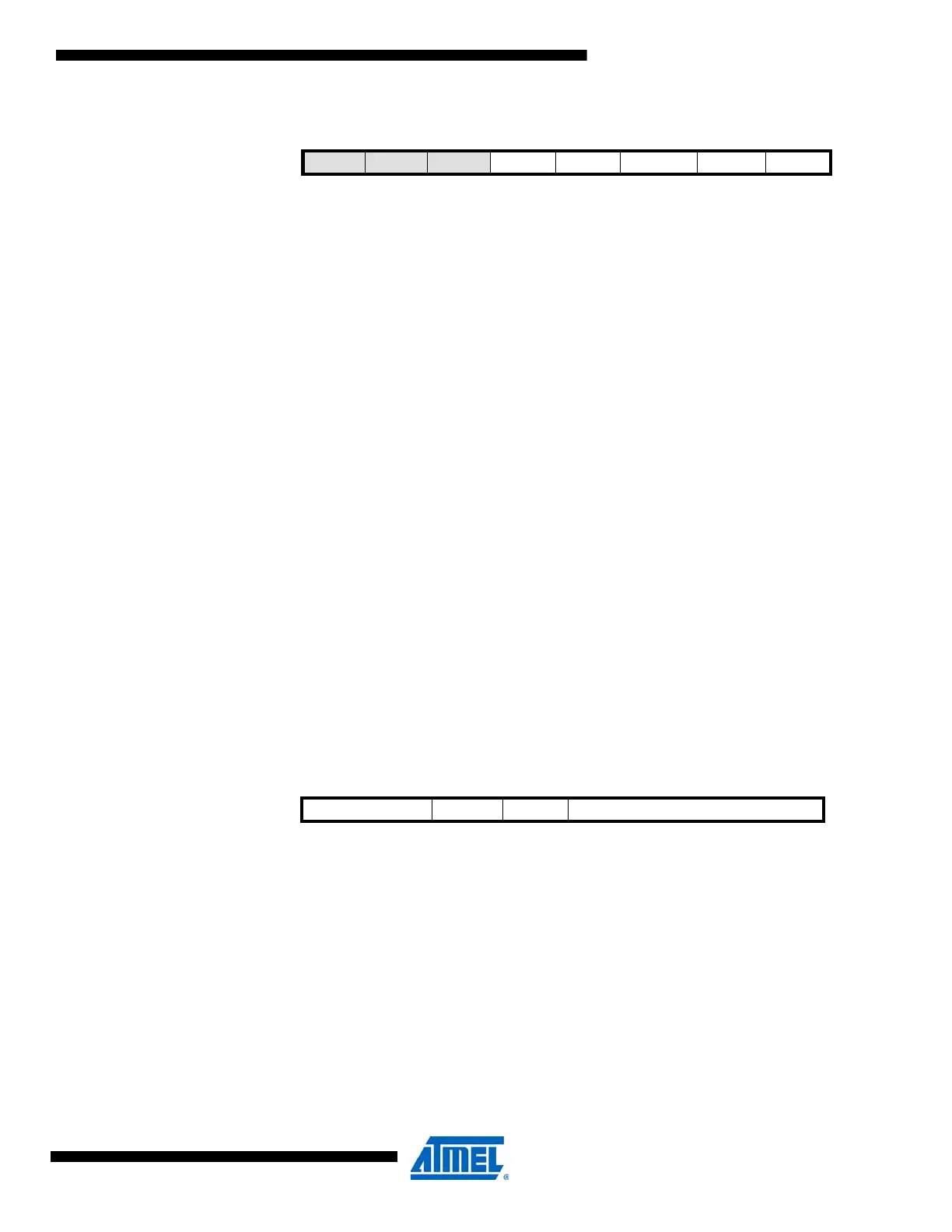

7.10.3 XOSCCTRL – XOSC Control register

• Bit 7:6 – FRQRANGE[1:0]: 0.4 - 16MHz Crystal Oscillator Frequency Range Select

These bits select the frequency range for the connected crystal oscillator according to Table 7-7

on page 98.

Bit 765 4 3 2 1 0

+0x01 – – – PLLRDY XOSCRDY RC32KRDY RC32MRDY RC2MRDY STATUS

Read/Write R R R R R R R R

Initial Value 0 0 0 0 0 0 0 0

Bit 7 6 5 43210

+0x02 FRQRANGE[1:0] X32KLPM XOSCPWR XOSCSEL[3:0] XOSCCTRL

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value 0 0 0 0 0 0 0 0

Loading...

Loading...