63

8331B–AVR–03/12

Atmel AVR XMEGA AU

5.14.2 CTRLB – Control register B

• Bit 7 – CHBUSY: Channel Busy

When the DMA channel starts a DMA transaction, the CHBUSY flag will be read as one. This

flag is automatically cleared when the DMA channel is disabled, when the channel transaction

complete interrupt flag is set or when the channel error interrupt flag is set.

• Bit 6 – CHPEND: Channel Pending

If a block transfer is pending on the DMA channel, the CHPEND flag will be read as one. This

flag is automatically cleared when the transfer starts or if the transfer is aborted.

• Bit 5 – ERRIF: Error Interrupt Flag

If an error condition is detected on the DMA channel, the ERRIF flag will be set and the optional

interrupt is generated. Since the DMA channel error interrupt shares the interrupt address with

the DMA channel n transaction complete interrupt, ERRIF will not be cleared when the interrupt

vector is executed. This flag is cleared by writing a one to this location.

• Bit 4 – TRNIF: Channel n Transaction Complete Interrupt Flag

When a transaction on the DMA channel has been completed, the TRNIF flag will be set and the

optional interrupt is generated. When repeat is not enabled, the transaction is complete and

TRNIFR is set after the block transfer. When unlimited repeat is enabled, TRNIF is also set after

each block transfer.

Since the DMA channel transaction n complete interrupt shares the interrupt address with the

DMA channel error interrupt, TRNIF will not be cleared when the interrupt vector is executed.

This flag is cleared by writing a one to this location.

• Bit 3:2 – ERRINTLVL[1:0]: Channel Error Interrupt Level

These bits enable the interrupt for DMA channel transfer errors and select the interrupt level, as

described in ”Interrupts and Programmable Multilevel Interrupt Controller” on page 134. The

enabled interrupt will trigger for the conditions when ERRIF is set.

• Bit 1:0 – TRNINTLVL[1:0]: Channel Transaction Complete Interrupt Level

These bits enable the interrupt for DMA channel transaction completes and select the interrupt

level, as described in ”Interrupts and Programmable Multilevel Interrupt Controller” on page 134.

The enabled interrupt will trigger for the conditions when TRNIF is set.

5.14.3 ADDRCTRL – Address Control register

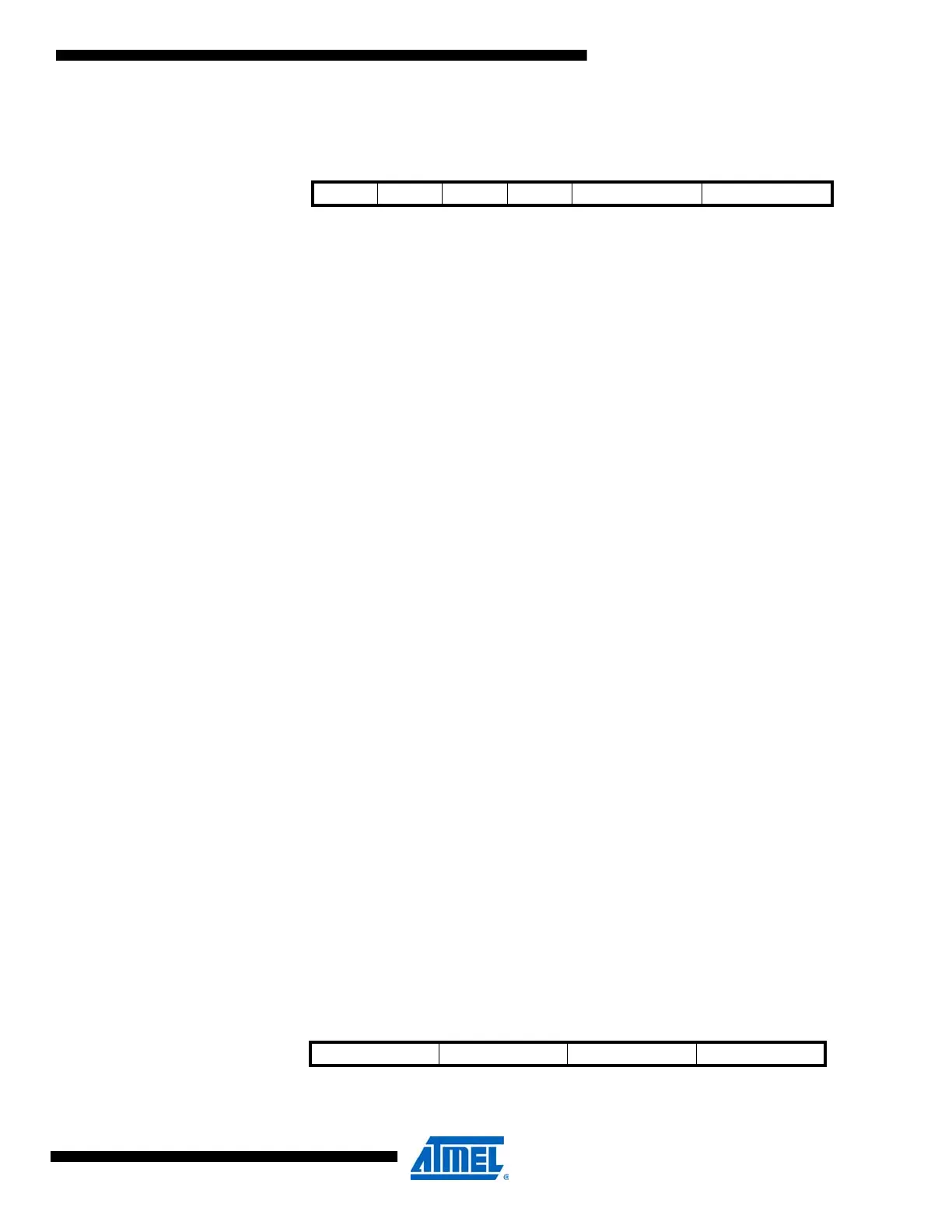

Bit 76543210

+0x01 CHBUSY CHPEND ERRIF TRNIF ERRINTLVL[1:0] TRNINTLVL[1:0] CTRLB

Read/Write R R R/W R/W R/W R/W R/W R/W

Initial Value 0 0 0 0 0 0 0 0

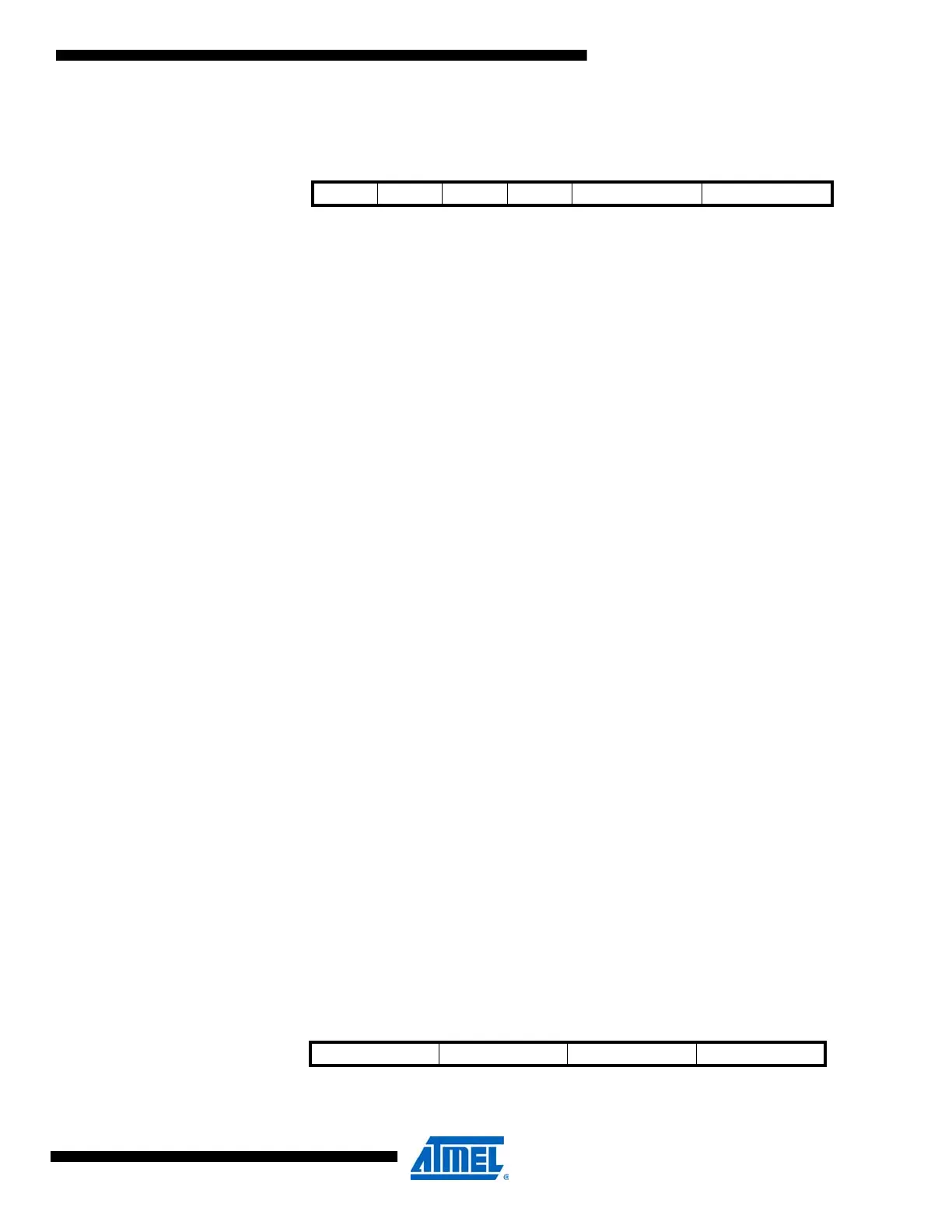

Bit 76543210

+0x02 SRCRELOAD[1:0] SRCDIR[1:0] DESTRELOAD[1:0] DESTDIR[1:0] ADDRCTRL

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value00000000

Loading...

Loading...