64

8331B–AVR–03/12

Atmel AVR XMEGA AU

• Bit 7:6 – SRCRELOAD[1:0]: Channel Source Address Reload

These bits decide the DMA channel source address reload according to Table 5-5. A write to

these bits is ignored while the channel is busy.

• Bit 5:4 – SRCDIR[1:0]: Channel Source Address Mode

These bits decide the DMA channel source address mode according to Table 5-6. These bits

cannot be changed if the channel is busy.

• Bit 3:2 – DESTRELOAD[1:0]: Channel Destination Address Reload

These bits decide the DMA channel destination address reload according to Table 5-7 on page

64. These bits cannot be changed if the channel is busy.

• Bit 1:0 – DESTDIR[1:0]: Channel Destination Address Mode

These bits decide the DMA channel destination address mode according to Table 5-8 on page

65. These bits cannot be changed if the channel is busy.

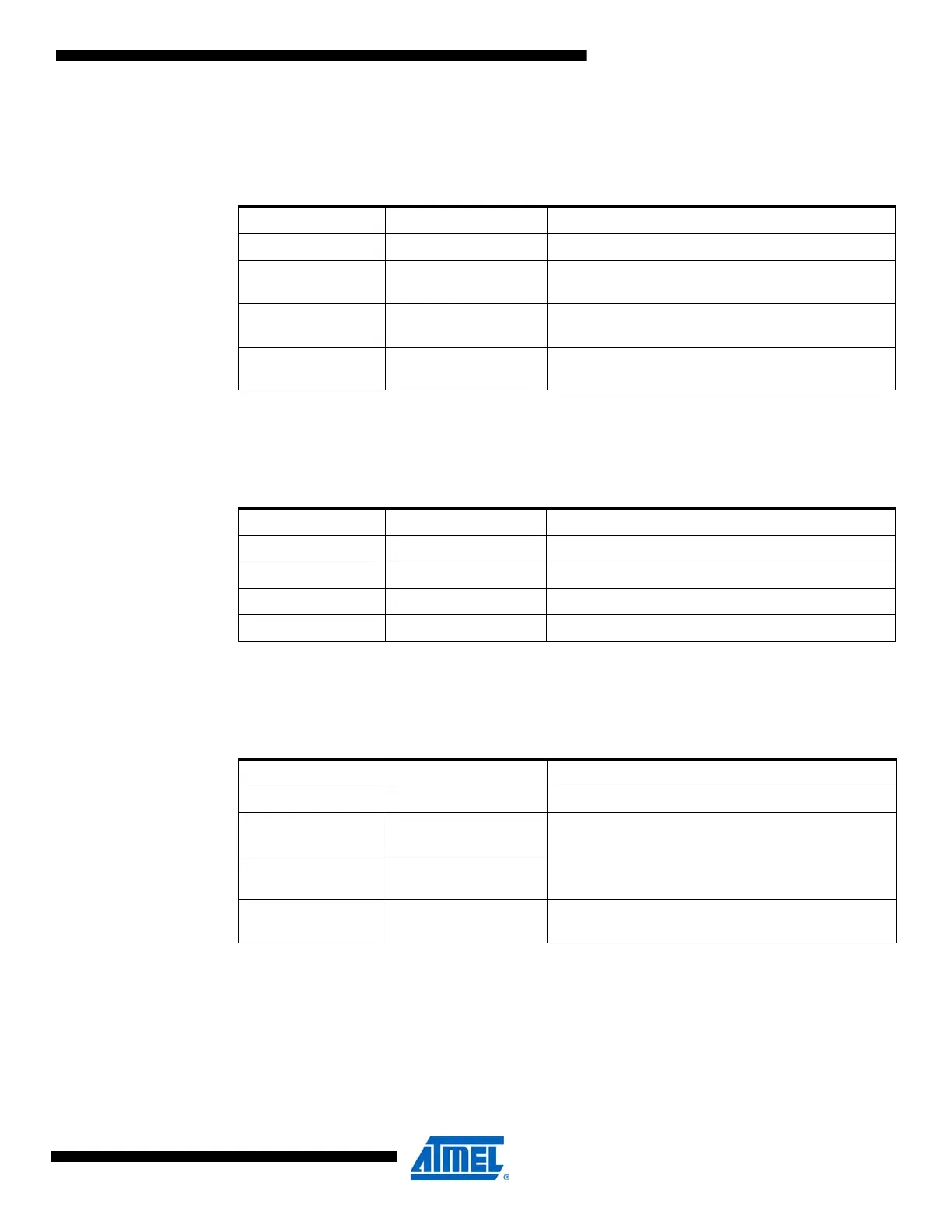

Table 5-5. DMA channel source address reload settings.

SRCRELOAD[1:0] Group Configuration Description

00 NONE No reload performed.

01 BLOCK

DMA source address register is reloaded with initial

value at end of each block transfer.

10 BURST

DMA source address register is reloaded with initial

value at end of each burst transfer.

11 TRANSACTION

DMA source address register is reloaded with initial

value at end of each transaction.

Table 5-6. DMA channel source address mode settings.

SRCDIR[1:0] Group Configuration Description

00 FIXED Fixed

01 INC Increment

10 DEC Decrement

11 - Reserved

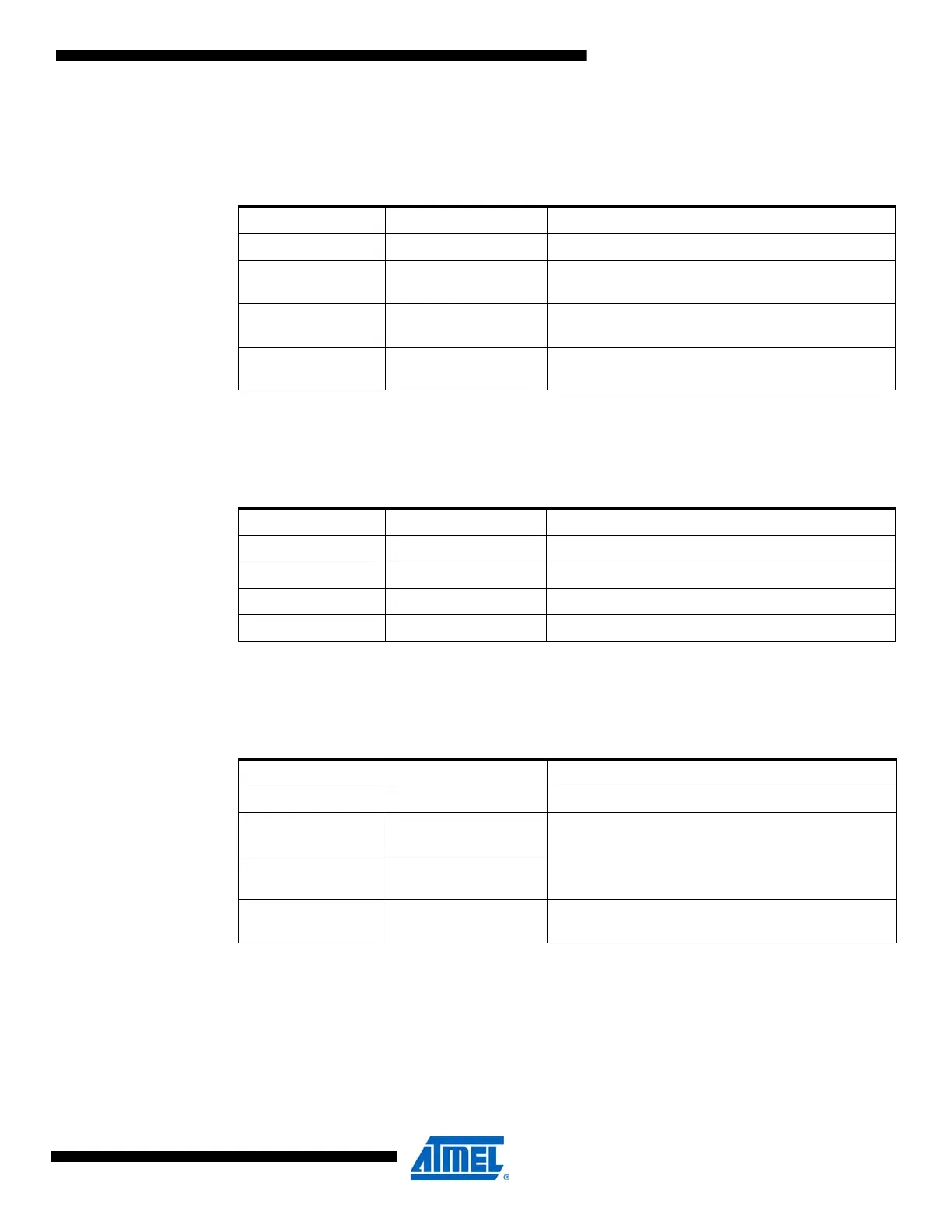

Table 5-7. DMA channel destination address reload settings.

DESTRELOAD[1:0] Group Configuration Description

00 NONE No reload performed.

01 BLOCK

DMA channel destination address register is reloaded

with initial value at end of each block transfer.

10 BURST

DMA channel destination address register is reloaded

with initial value at end of each burst transfer.

11 TRANSACTION

DMA channel destination address register is reloaded

with initial value at end of each transaction.

Loading...

Loading...