350

8331B–AVR–03/12

Atmel AVR XMEGA AU

27.10.6 SDRAMCTRLC – SDRAM Control register C

• Bit 7:6 – WRDLY[1:0]: SDRAM Write Recovery Delay

These bits select the write recovery time in number of Clk

PER2

cycles, according to Table 27-15

on page 349.

• Bit 5:3 – ESRDLY[2:0]: SDRAM Exit Self-refresh to Active Delay

This field defines the delay between CKE set high and an ACTIVE command in a number of

Clk

PER2

cycles, according to Table 27-19 on page 351.

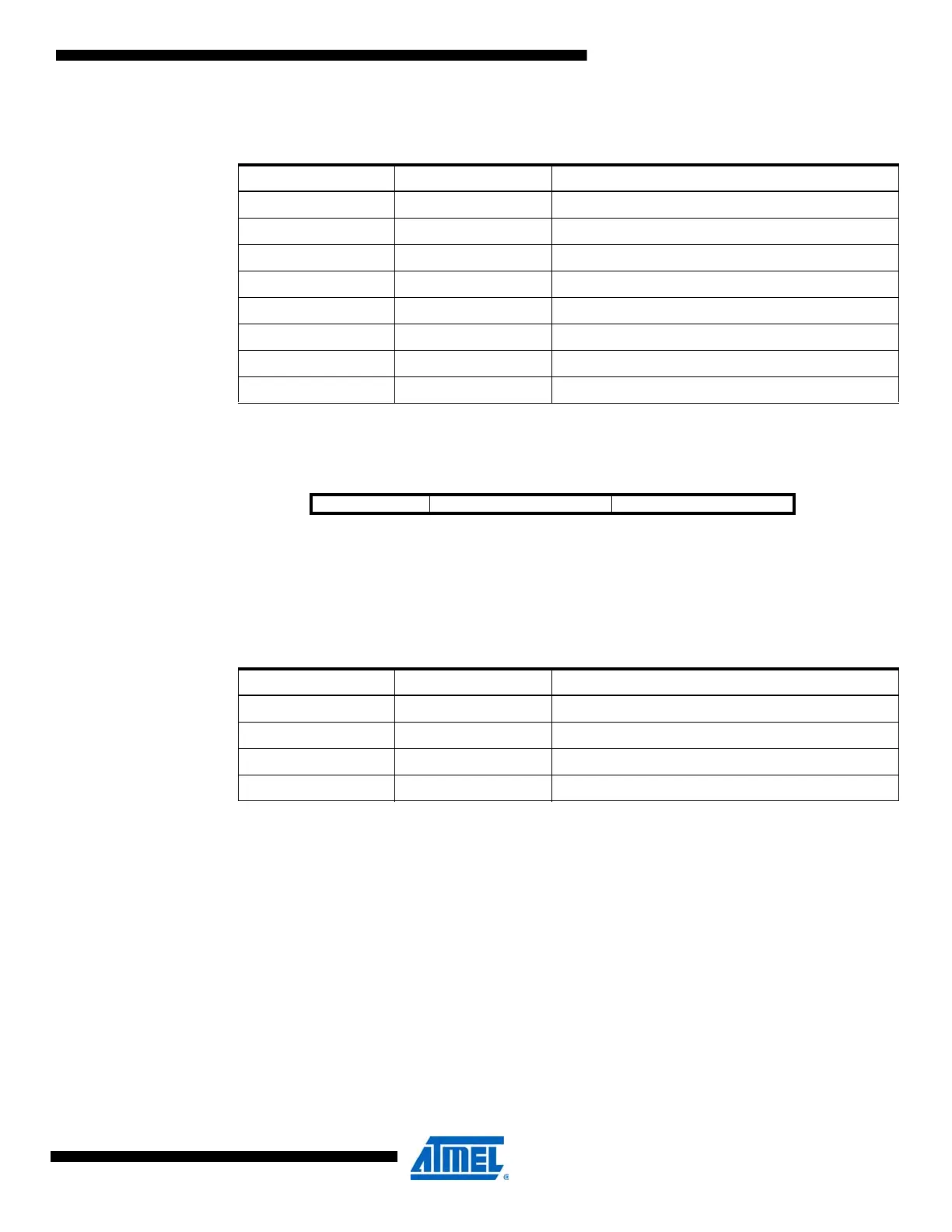

Table 27-17. SDRAM row to precharge delay settings

RPDLY[2:0] Group Configuration Description

000 0CLK Zero Clk

PER2

cycles delay

001 1CLK One Clk

PER2

cycles delay

010 2CLK Two Clk

PER2

cycles delay

011 3CLK Three Clk

PER2

cycles delay

100 4CLK Four Clk

PER2

cycles delay

101 5CLK Five Clk

PER2

cycles delay

110 6CLK Six Clk

PER2

cycles delay

111 7CLK Seven Clk

PER2

cycles delay

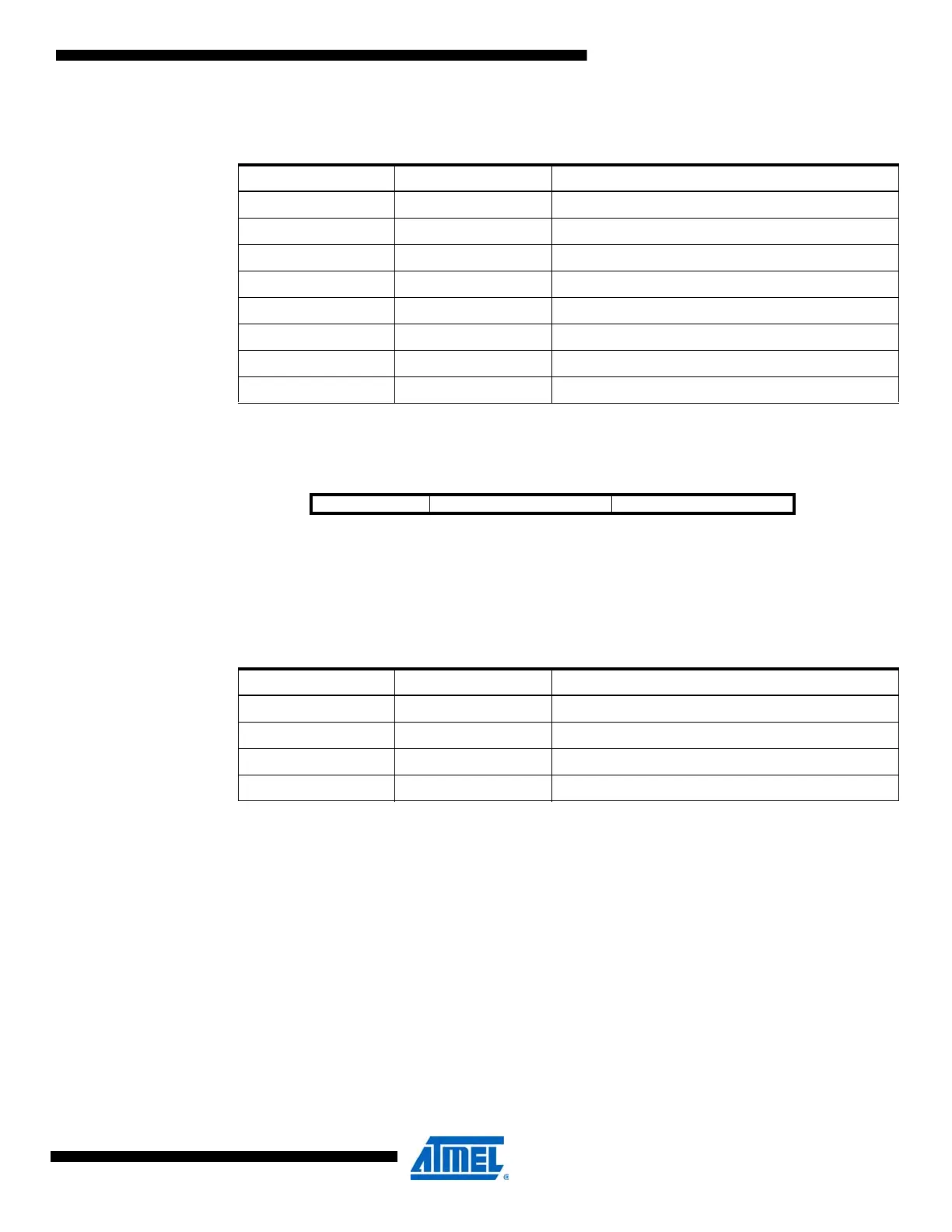

Bit 7654 3 2 10

+0x09 WRDLY[1:0] ESRDLY[1:0] ROWCOLDLY[1:0] SDRAMCTRLC

Read/Write R/W R/W R/W R/W R/W R/W R/W R/W

Initial Value0000 0 0 00

Table 27-18. SDRAM write recovery delay settings.

WRDLY[1:0] Group Configuration Description

00 0CLK Zero Clk

PER2

cycles delay

01 1CLK One Clk

PER2

cycles delay

10 2CLK Two Clk

PER2

cycles delay

11 3CLK Three Clk

PER2

cycles delay

Loading...

Loading...