311

8331B–AVR–03/12

Atmel AVR XMEGA AU

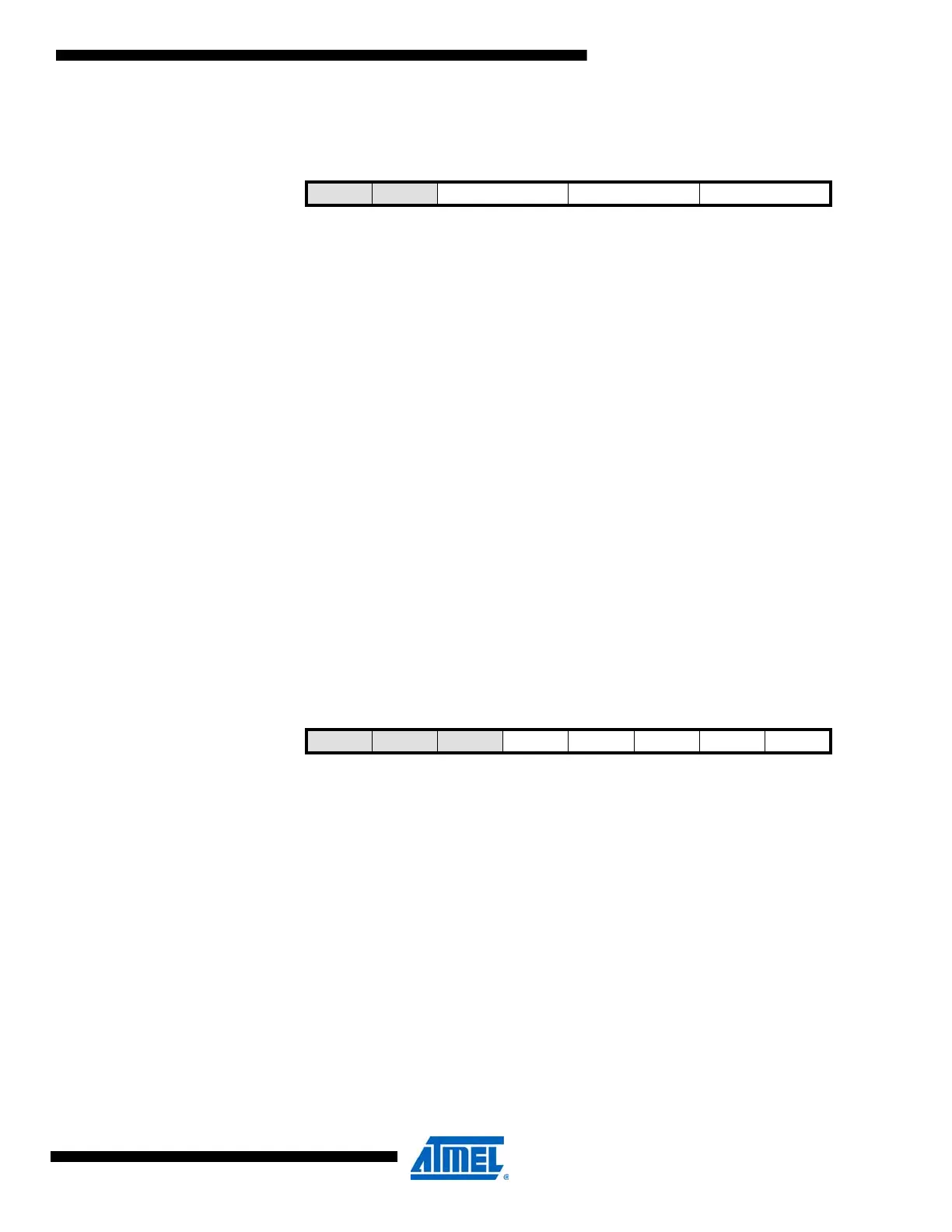

23.15.3 CTRLA – Control register A

• Bit 7:6 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 5:4 – RXCINTLVL[1:0]: Receive Complete Interrupt Level

These bits enable the receive complete interrupt and select the interrupt level, as described in

”Interrupts and Programmable Multilevel Interrupt Controller” on page 134. The enabled interrupt

will be triggered when the RXCIF flag in the STATUS register is set.

• Bit 3:2 – TXCINTLVL[1:0]: Transmit Complete Interrupt Level

These bits enable the transmit complete interrupt and select the interrupt level, as described in

”Interrupts and Programmable Multilevel Interrupt Controller” on page 134. The enabled interrupt

will be triggered when the TXCIF flag in the STATUS register is set.

• Bit 1:0 – DREINTLVL[1:0]: Data Register Empty Interrupt Level

These bits enable the data register empty interrupt and select the interrupt level, as described in

”Interrupts and Programmable Multilevel Interrupt Controller” on page 134. The enabled interrupt

will be triggered when the DREIF flag in the STATUS register is set.

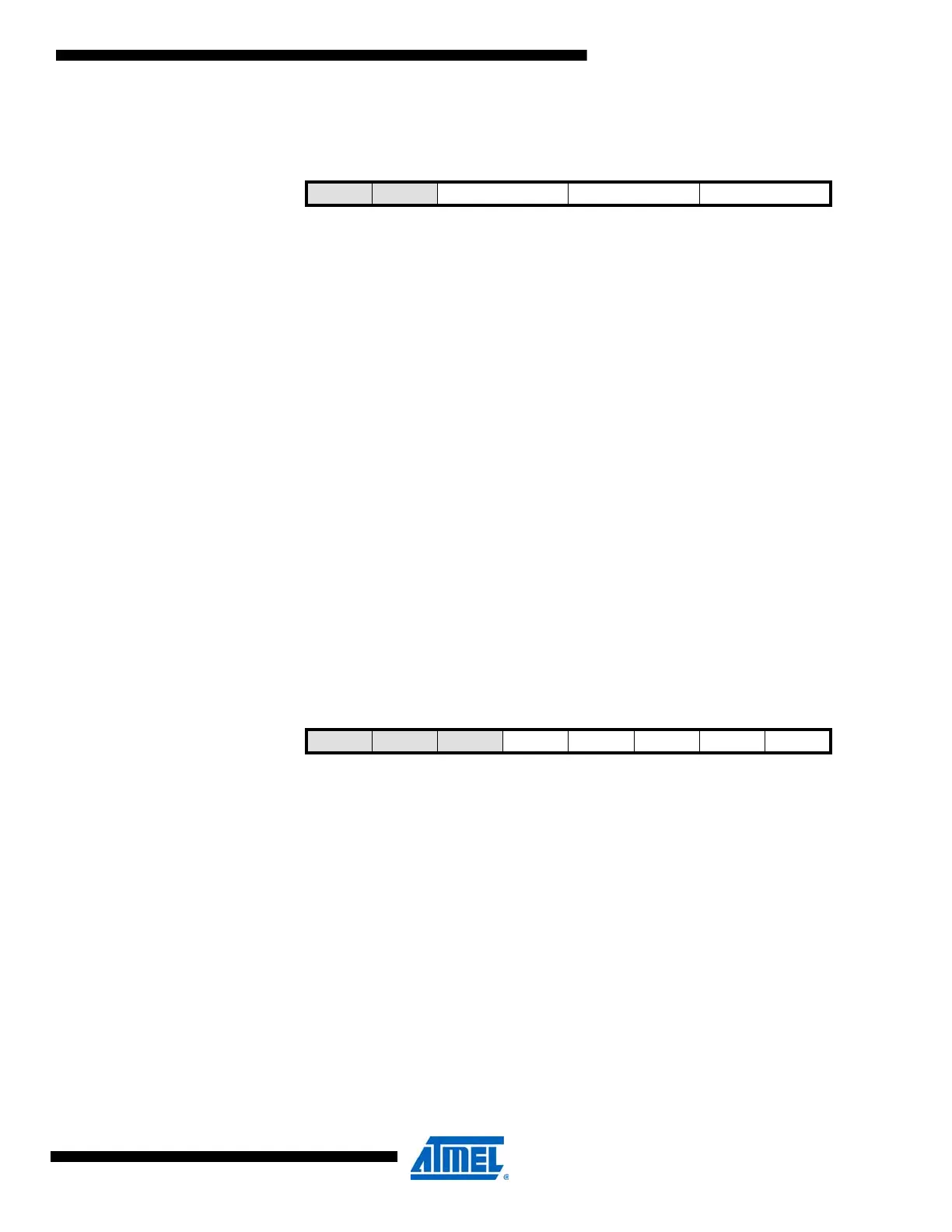

23.15.4 CTRLB – Control register B

• Bit 7:5 – Reserved

These bits are unused and reserved for future use. For compatibility with future devices, always

write these bits to zero when this register is written.

• Bit 4 – RXEN: Receiver Enable

Setting this bit enables the USART receiver. The receiver will override normal port operation for

the RxD pin, when enabled. Disabling the receiver will flush the receive buffer, invalidating the

FERR, BUFOVF, and PERR flags.

• Bit 3 – TXEN: Transmitter Enable

Setting this bit enables the USART transmitter. The transmitter will override normal port opera-

tion for the TxD pin, when enabled. Disabling the transmitter (writing TXEN to zero) will not

become effective until ongoing and pending transmissions are completed; i.e., when the transmit

Bit 76543210

+0x03 – – RXCINTLVL[1:0] TXCINTLVL[1:0] DREINTLVL[1:0] CTRLA

Read/Write R R R/W R/W R/W R/W R/W R/W

Initial Value00000000

Bit 76543210

+0x04 – – – RXEN TXEN CLK2X MPCM TXB8 CTRLB

Read/Write R R R R/W R/W R/W R/W R/W

Initial Value00000000

Loading...

Loading...