NXP Semiconductors

UM11227

NTM88 family of tire pressure monitor sensors

UM11227 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2020. All rights reserved.

User manual Rev. 6 — 24 April 2020

118 / 205

Table 103. RFCR0 register field descriptions

Field Description

7:0

BPS[7:0]

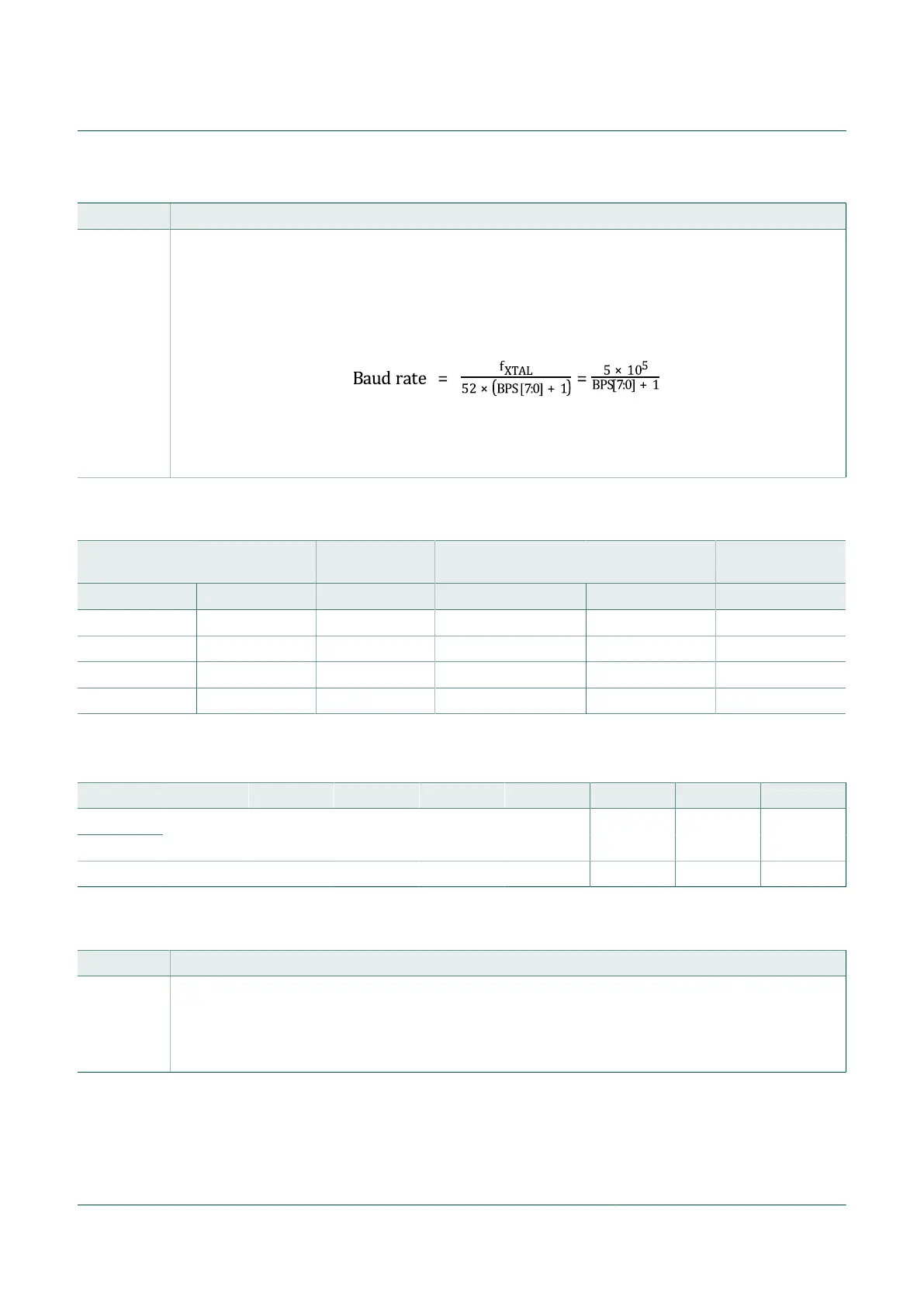

The BPS[7:0] bits select a divider for the incoming external crystal clock to generate the baud rate. The

operating range of BPS[7:0] is $00 up to $FF. Reading BPS[7:0] provides the value written. This results in a

baud rate from 1953 up to 500,000 bits per second, when the external crystal clock is 26 MHz.

The conversion from the decimal value of the BPS[7:0] bits to the baud rate is given as described in the

following equation. Power-on-reset forces BPS[7:0] to a value of $34 (decimal 52), and results in baud rate

of 9434 bits per second, assuming external crystal clock is typical 26 MHz.

Where:

f

XTAL

= External crystal frequency in Hz = 26 MHz

$34 = Result of Reset

Table 104. Data rate option examples

Data Rate

BPS[7:0]

Decimal Value

Data Rate

BPS[7:0] Decimal

Value

Target Nominal f

XTAL

= 26 MHz Target Nominal f

XTAL

= 26 MHz

2000 bit/s 2000.0 249 4800 bit/s 4807.7 103

2400 bit/s 2403.8 207 5000 bit/s 5000.0 99

4000 bit/s 4000.0 124 9600 bit/s 9615.4 51

4500 bit/s 4504.5 110 19200 bit/s 19230.8 25

10.16.11.2 RFM control 1 register (RFCR1)

Table 105. RFM control 1 register (RFCR1) (address $1831)

Bit 7 6 5 4 3 2 1 0

R

W

FRM7 FRM6 FRM5 FRM4 FRM3 FRM2 FRM1 FRM0

Reset ($00) 0 0 0 0 0 0 0 0

Table 106. RFCR1 register field descriptions

Field Description

7:0

FRM[7:0]

The 8 bits FRM[7:0] select the number of bits in each datagram. The number of bits is determined by the

binary value of the FRM[7:0] bits plus one. This makes the range of bits from 2 to 256. A value of $00 for the

FRM[7:0] control bits will result in no frames being sent. The FRM[7:0] control bits are cleared by RFMRST

signal.

$00 = Result of Reset

Loading...

Loading...