NXP Semiconductors

UM11227

NTM88 family of tire pressure monitor sensors

UM11227 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2020. All rights reserved.

User manual Rev. 6 — 24 April 2020

158 / 205

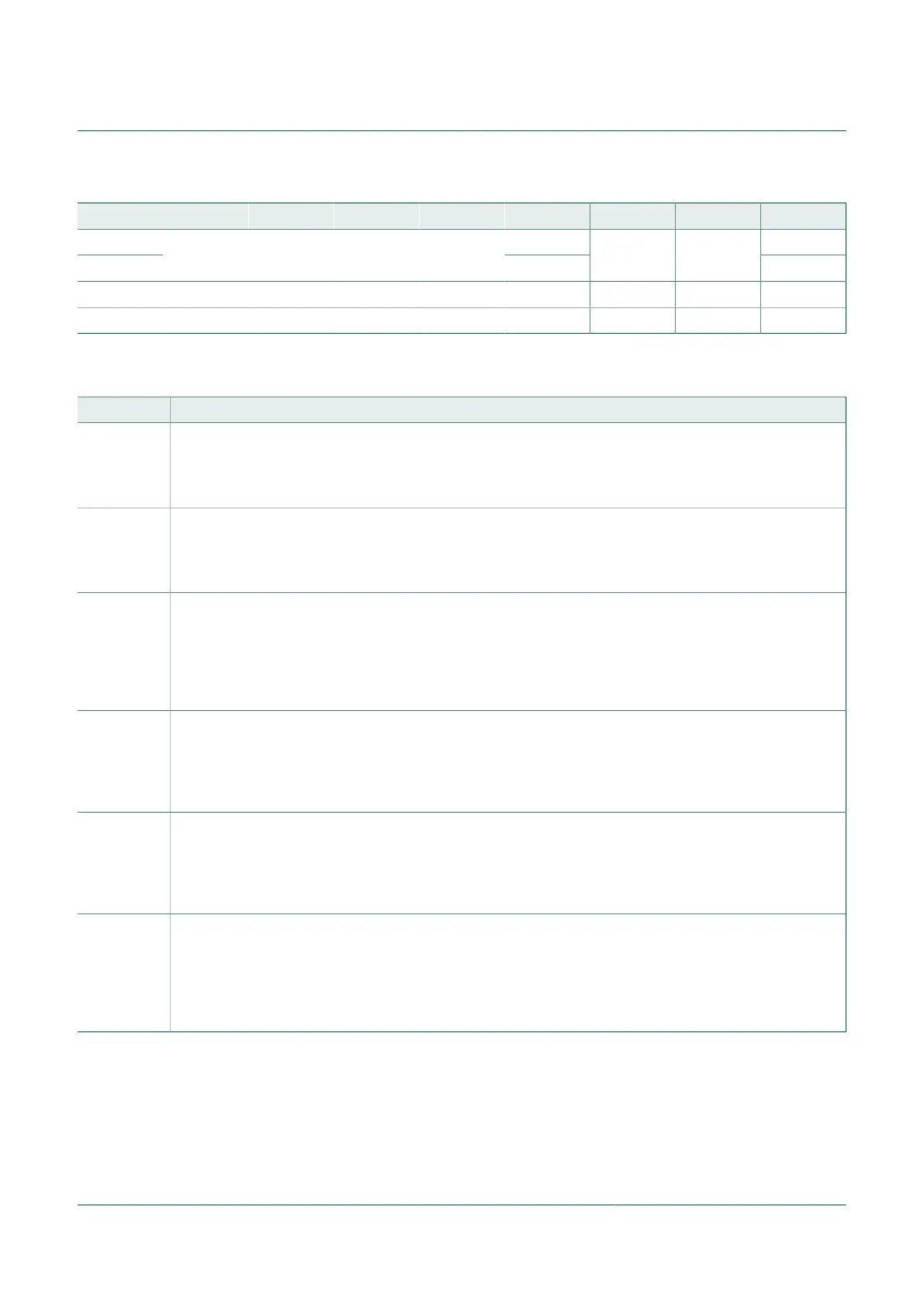

Table 164. SIM option 1 register (SIMOPT1) (address $1802)

Bit 7 6 5 4 3 2 1 0

R 0 0

W

COPE COPCLKS STOPE RFEN

—

SPIEN BKGDPE

—

Reset 1 0 0 U 0 0 1 1

POR ($83) 1 0 0 0 0 0 1 1

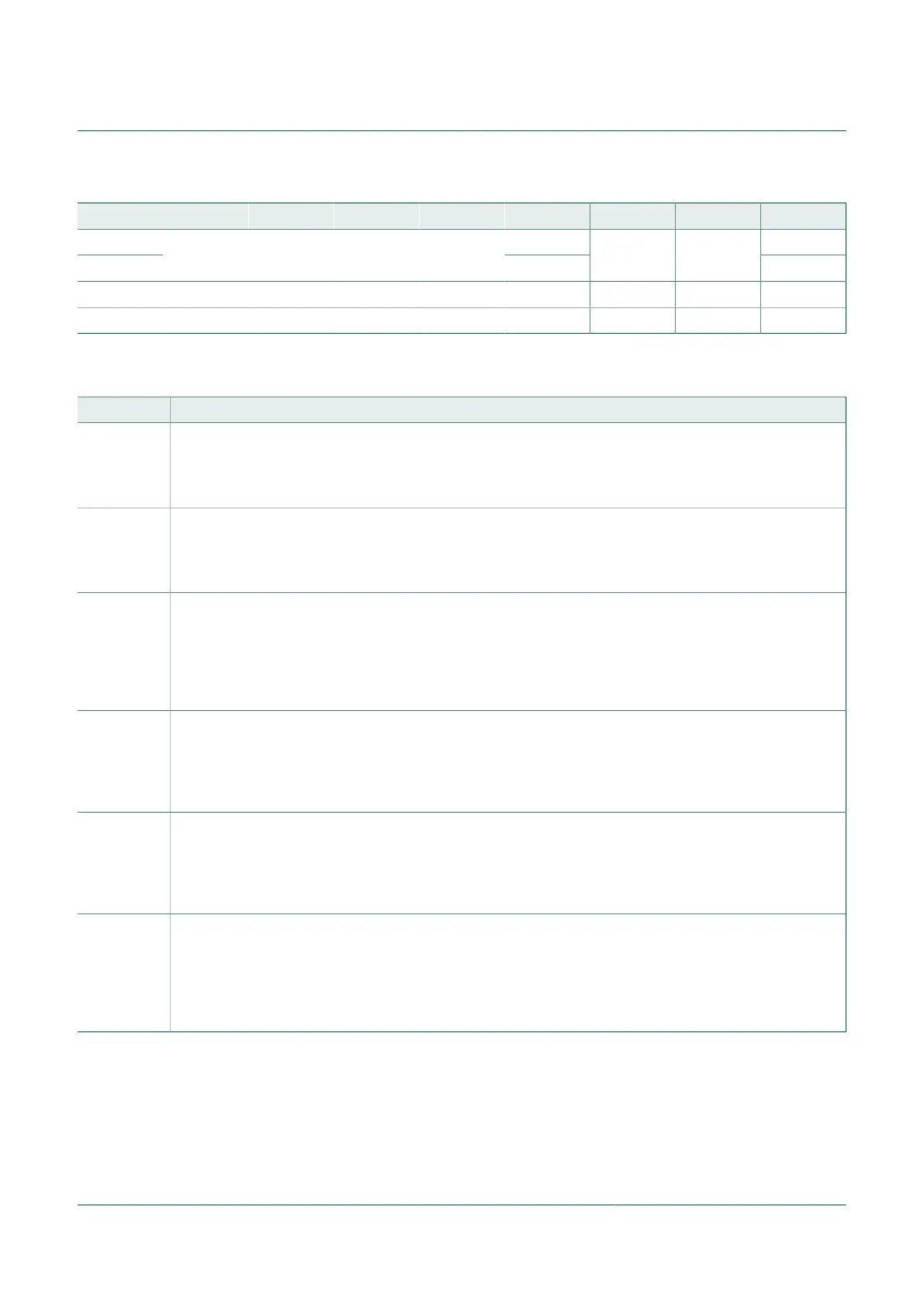

Table 165. SIMOPT1 register field descriptions

Field Description

7

COPE

COPE — COP Enable Bit

The COPE bit enables the COP.

0 = COP disabled

1 = COP enabled; Result of Reset

6

COPCLKS

COPCLKS — COP Clock Selection

This bit selects the clock source of the COP watchdog.

0 = Internal 1 kHz clock is sourced to COP; Result of Reset

1 = Bus clock is sourced to COP.

5

STOPE

STOPE — STOP Enable Bit

The STOPE bit enables the STOP instruction. If the STOP instruction is disabled and a STOP instruction is

executed, then an illegal opcode reset occurs. The STOPE bit is writable only once after each exit from a

system reset.

0 = STOP instruction disabled; Result of Reset

1 = STOP instruction enabled.

4

RFEN

RFEN — RF Transmitter Enable Bit

This bit enables the RF module.

0 = RF disabled; Result of power-on reset; Existing state retained from resets of Stop1 exit, low voltage

detection, external pin, COP, PWU, illegal opcode, illegal address, soft reset, and back-ground debugger.

1 = RF enabled.

2

SPIEN

SPIEN — SPI Enable Bit

This bit enables the SPI module. Result of enabling the SPI is the Port A is configured for SPI IOs. Also, the

SPI is enabled if the PTA0 pin is held low for > tSPI_EN as the POR is released.

0 = SPI disabled; Result of Reset

1 = SPI enabled.

1

BKGDPE

BKGDPE — BKGD Pin Enable Bit

When BKGD/MS is shared with general-purpose I/O through chip-level hookup, The BKGDPE bit enables

the BKGD/MS pin to function as BKGD. When the BKGDPE bit is clear, the pin functions as general-

purpose I/O, which must be implemented as output-only.

0 = BKGD pin disabled

1 = BKGD pin enabled; Result of Reset

Loading...

Loading...