NXP Semiconductors

UM11227

NTM88 family of tire pressure monitor sensors

UM11227 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2020. All rights reserved.

User manual Rev. 6 — 24 April 2020

73 / 205

The central component of the TPM1 is the 16-bit counter that can operate as a free-

running counter, a modulo counter, or an up- /down-counter when the TPM1 is

configured for center-aligned PWM. The TPM1 counter (when operating in normal

up-counting mode) provides the timing reference for the input capture, output

compare, and edge-aligned PWM functions. The timer counter modulo registers,

TPMMODH:TPMMODL, control the modulo value of the counter. (The values 0x0000

or 0xFFFF effectively make the counter free running.) Software can read the counter

value at any time without affecting the counting sequence. Any write to either byte of the

TPMCNT counter resets the counter regardless of the data value written.

All TPM1 channels are programmable independently as input capture, output compare,

or buffered edge-aligned PWM channels.

10.13.2 External signal description

When any pin associated with the timer is configured as a timer input, a passive pullup

can be enabled. After reset, the TPM1 modules are disabled and all pins default to

general-purpose inputs with the passive pullups disabled.

Each TPM1 channel is associated with an I/O pin on the MCU. The function of this pin

depends on the configuration of the channel. In some cases, no pin function is needed

so the pin reverts to being controlled by general-purpose I/O controls. When a timer has

control of a port pin, the port data and data direction registers do not affect the related

pin(s). See Section 7 "Pinning information" for additional information about shared pin

functions.

10.13.3 TPM register descriptions

10.13.3.1 Timer status and control register (TPMSC)

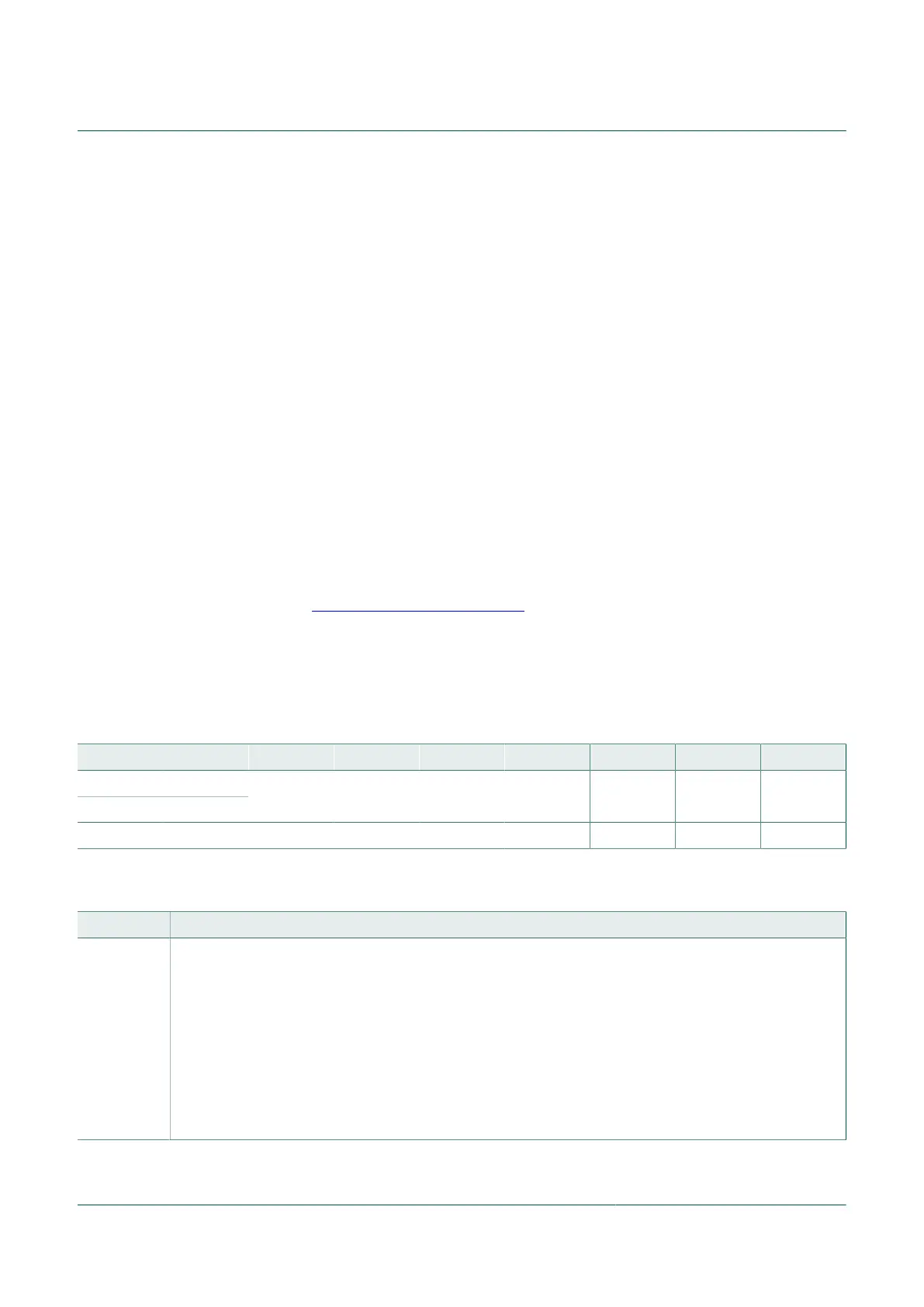

Table 45. Timer status and control register (TPMSC) (address $0010)

Bit 7 6 5 4 3 2 1 0

R TOF

W —

TOIE CPWMS CLKSB CLKSA PS2 PS1 PS0

Reset ($00) 0 0 0 0 0 0 0 0

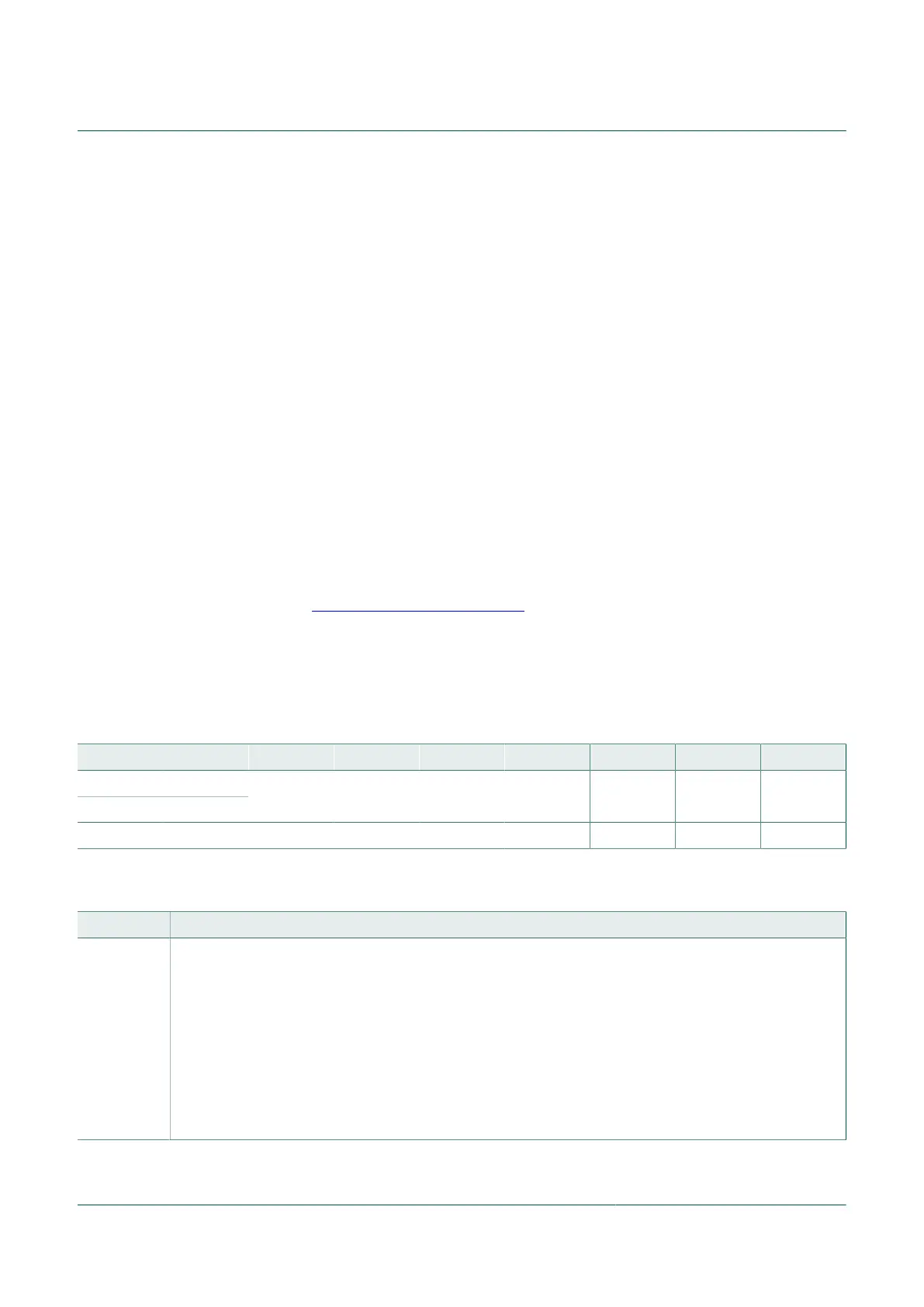

Table 46. TPMSC register field descriptions

Field Description

7

TOF

TOF – Timer Overflow Flag

This read-only TOF bit is set when the TPM1 counter changes to 0000 after reaching the modulo value

programmed in the TPM1 counter modulo registers. When the TPM1 is configured for CPWM, TOF is set

after the counter has reached the value in the modulo register, at the transition to the next lower count

value. Clear TOF by reading the TPM1 status and control register when TOF is set and then writing a 0 to

TOF. If another TPM1 overflow occurs before the clearing sequence is complete, the sequence is reset so

TOF would remain set after the clear sequence was completed for the earlier TOF. Writing a 1 to TOF has

no effect.

0 = TPM1 counter has not reached modulo value or overflow; Result of power-on reset. Existing state will

remain after all other types of reset.

1 = TPM1 counter has overflowed

Loading...

Loading...