NXP Semiconductors

UM11227

NTM88 family of tire pressure monitor sensors

UM11227 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2020. All rights reserved.

User manual Rev. 6 — 24 April 2020

97 / 205

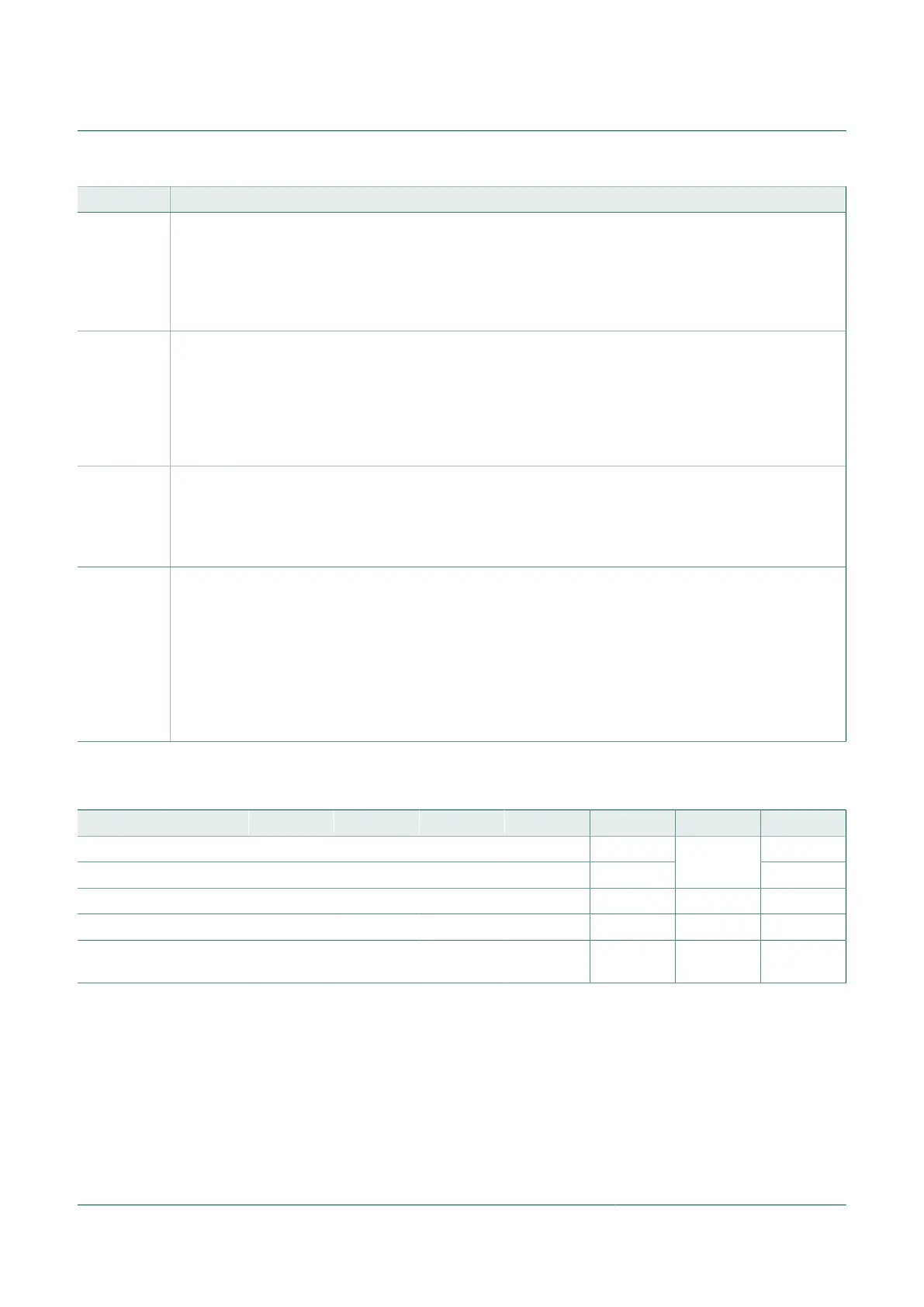

Field Description

4

LFIDIE

LFIDIE – LFR ID Detect Interrupt Enable

This read/write bit enables interrupts to be requested when the LFR detects a match to the wake-up ID code

selected in the LFIDH:L registers.

0 = LFIDF interrupts disabled; Use software polling; Result of power on or LFR reset. Existing state remains

after all other reset types.

1 = LFIDF interrupts are enabled. If LFIDIE is set, then an interrupt is requested when LFIDF = 1.

3

DCEN

DCEN – LF Digital Decode Enable

This read/write bit enables the data processing by the digital decoder. When disabled, the frame format

(Manchester, data-rate, SYNC, data) is not checked. There is no more error flag assertion (data, error, ID,

etc.). The MCU should then poll the LFDO bit to extract from the analog detector the bit stream.

0 = Digital decoder is disabled.

1 = Digital decoder is enabled; Result of power on or LFR reset. Existing state remains after all other reset

types.

2

VALEN

VALEN – LF Carrier Validation Enable

This read/write bit enables the carrier validation process.

0 = Carrier Validation disabled.

1 = Carrier Validation enabled; Result of power on or LFR reset. Existing state remains after all other reset

types.

1:0

TIMOUT[1:0]

TIMOUT[1:0] – Synchronization Time out Selection

The two bits TIMOUT[1:0] select the period of time that the LFR will search for a SYNC pattern in the

data mode. If the SYNC pattern is not detected the LFR will be turned off after this delay time. These time

intervals are clocked by the internal LFRO clock.

0 0 = SYNC word is continuously searched — no timeout.

0 1 = SYNC search time set to nominal 8 milliseconds.

1 0 = SYNC search time set to nominal 24 milliseconds.

1 1 = SYNC search time set to nominal 48 milliseconds; Result of power on or LFR reset. Existing state

remains after all other reset types.

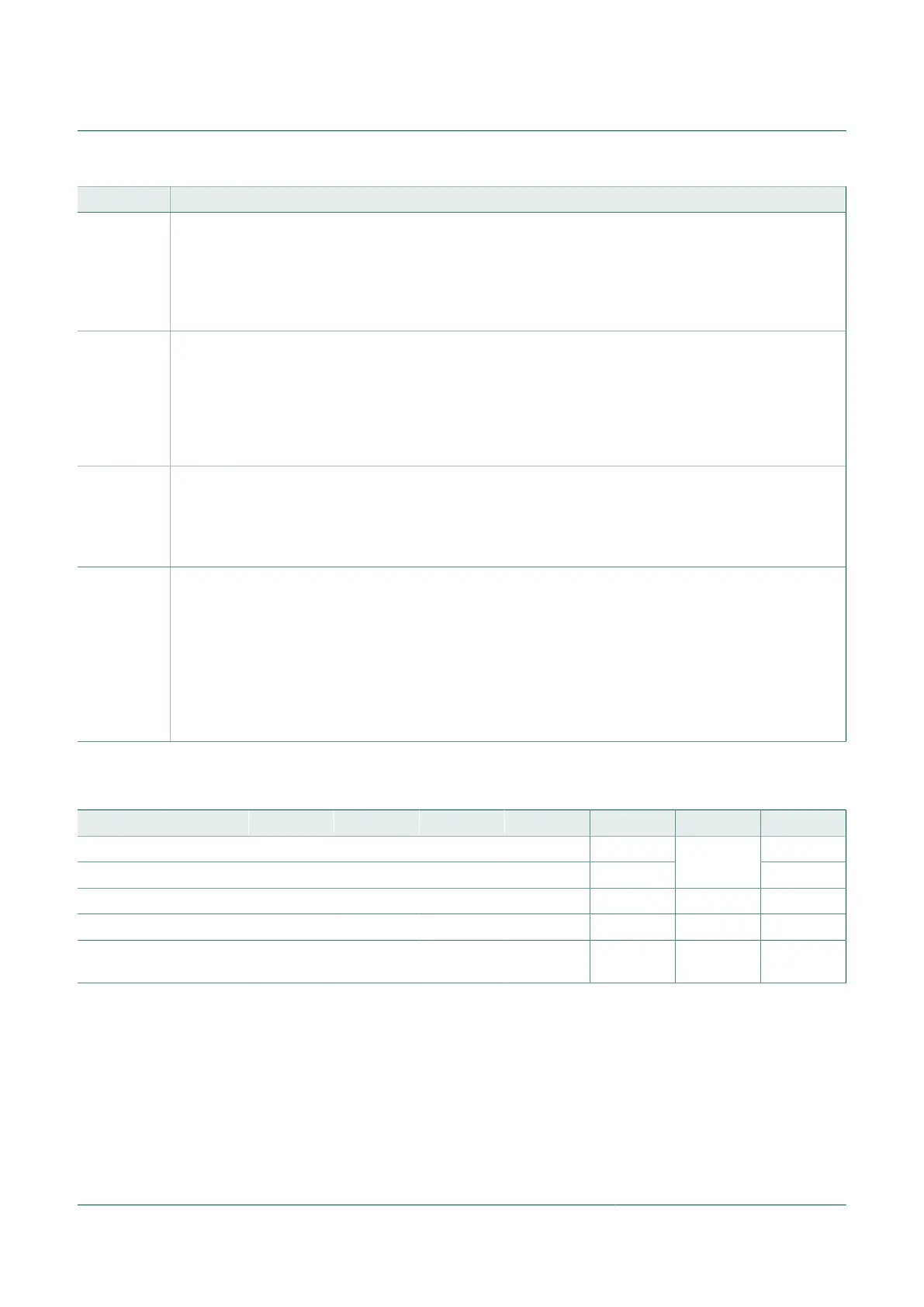

10.15.17.5 LF receiver status register (LFS)

Table 83. LF receiver status register (LFS) (address $0024)

Bit 7 6 5 4 3 2 1 0

R LFDRF LFERF LFCDF LFIDF LFOVF LFEOMF 0

W — — — — — —

LPSM

LFIAK

Reset U U U U U U U U

POR ($02) 0 0 0 0 0 0 1 0

LFR Soft

Reset ($02)

0 0 0 0 0 0 1 0

Loading...

Loading...