NXP Semiconductors

UM11227

NTM88 family of tire pressure monitor sensors

UM11227 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2020. All rights reserved.

User manual Rev. 6 — 24 April 2020

121 / 205

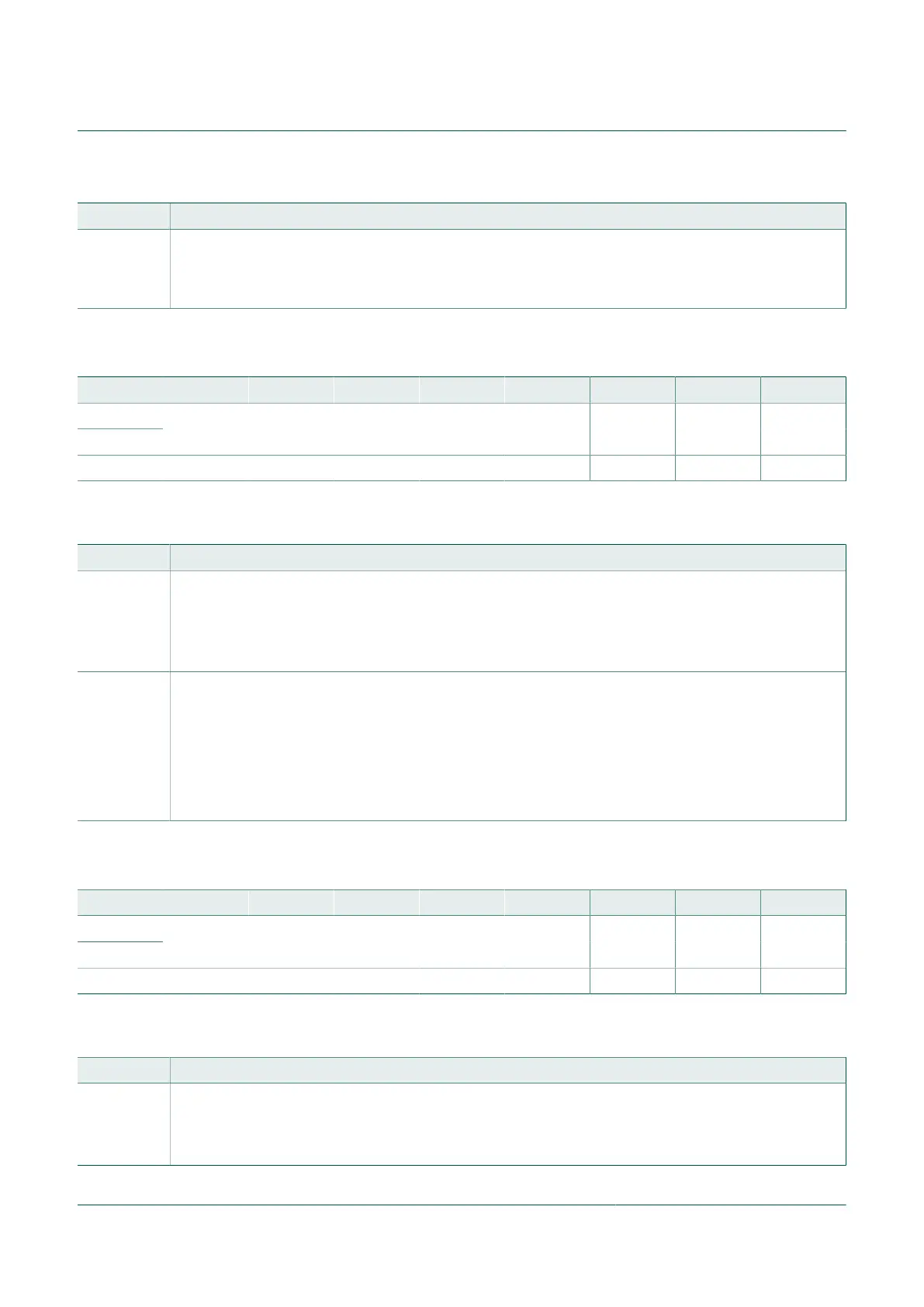

Table 112. RFCR4 register field descriptions

Field Description

7:0

RFBT[7:0]

RFBT[7:0] – The 8 bits RFBT[7:0] select the interframe timing between multiple frames of transmission. The

base time value is equal to a nominal one millisecond for each count of the RFBT[7:0] bits. The RFBT[7:0]

control bits are cleared by the RFMRST signal and must be set to either 0 or between 5 and 255.

$80 = Result of Reset

10.16.11.6 RFM control 5 register (RFCR5)

Table 113. RFM control 5 register (RFCR5) (address $1835)

Bit 7 6 5 4 3 2 1 0

R

W

BOOST LFSR6 LFSR5 LFSR4 LFSR3 LFSR2 LFSR1 LFSR0

Reset ($00) 0 0 0 0 0 0 0 0

Table 114. RFCR5 register field descriptions

Field Description

7

BOOST

BOOST – VCO Power Consumption Boost Control

This bit controls the VCO power consumption in order to decrease the phase noise required by the

Japanese regulation. The BOOST control bit is cleared by the RFMRST signal.

0 = The VCO runs at its lower power consumption level (higher phase noise); Result of Reset

1 = The VCO runs at its higher power consumption level (lower phase noise).

6:0

LFSR[6:0]

LFSR[6:0] – Pseudo-Random timer

The 7 bits LFSR[6:0] select the current seed value of the LFSR when enabling pseudo-random timing

intervals when any of the LFSR[6:0] bits are set. The value written to this register is loaded into the actual

LFSR when the SEND bit is set. The time value is equal to a nominal one millisecond for each count of

the resulting LFSR[6:0] bits. A value of $00 placed in the LFSR causes the LFSR to stay at the $00 state

on each clocking of the LFSR. To cause the LFSR to cycle through its pseudo-random number sequence

requires that any value other than $00 be written to the LFSR[6:0] bits.

0 0 0 0 0 0 0 = Result of Reset

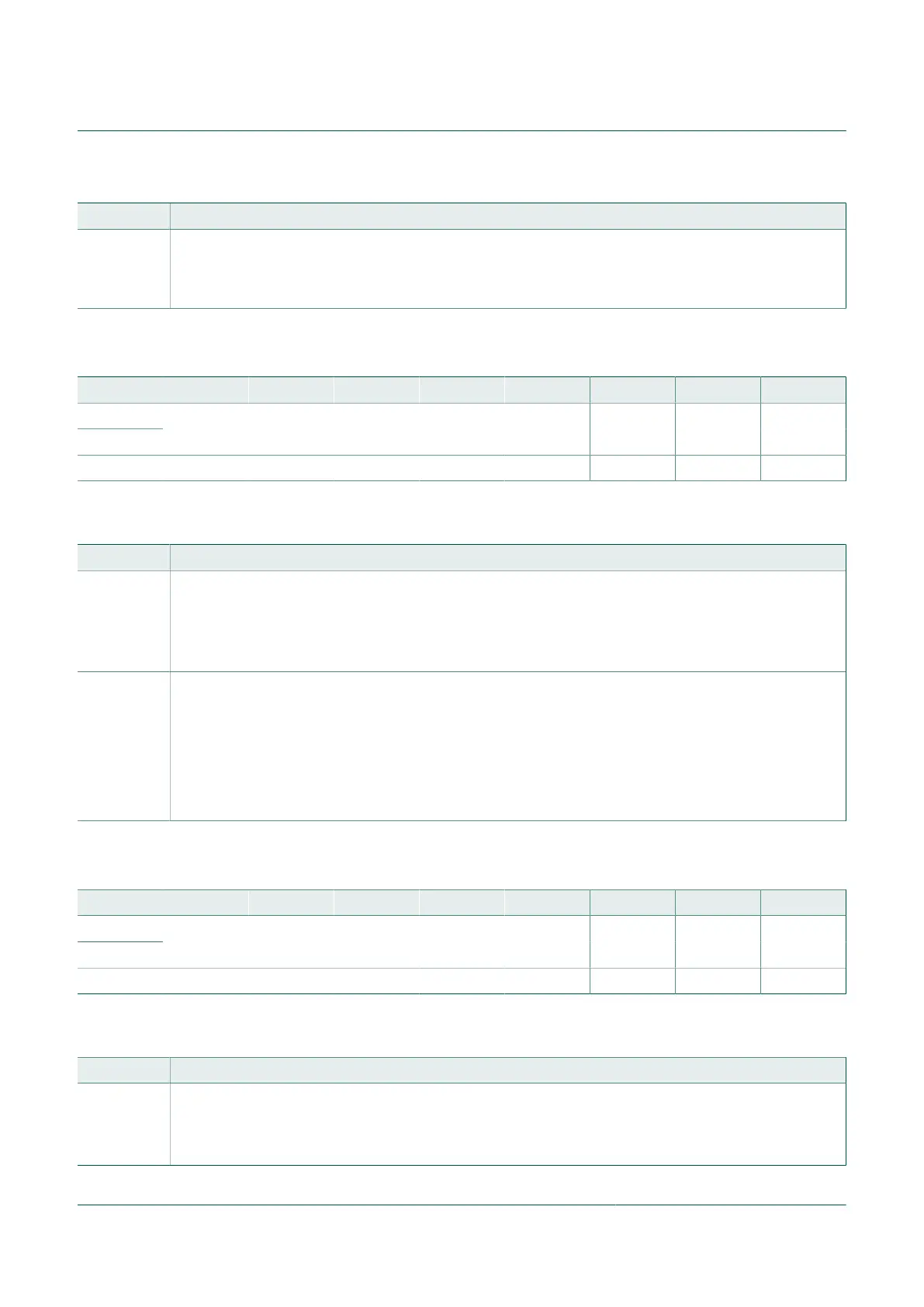

10.16.11.7 RFM control 6 register (RFCR6)

Table 115. RFM control 6 register (RFCR6) (address $1836)

Bit 7 6 5 4 3 2 1 0

R

W

VCO_

GAIN1

VCO_

GAIN0

RFFT5 RFFT4 RFFT3 RFFT2 RFFT1 RFFT0

Reset ($00) 1 0 0 0 0 0 0 0

Table 116. RFCR6 register field descriptions

Field Description

7:6

VCO_

GAIN[1:0]

VCO_GAIN[1:0] – VCO Gain Selection

The two bits VCO_GAIN[1:0] bit is set and the VCO_GAIN[0] bit is cleared by the RFMRST signal. VCO_

GAIN does not normally need to be adjusted by the end user.

1 0 = Result of Reset

Loading...

Loading...