NXP Semiconductors

UM11227

NTM88 family of tire pressure monitor sensors

UM11227 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2020. All rights reserved.

User manual Rev. 6 — 24 April 2020

168 / 205

10.23.3.3 PMC status and control 2 register (SPMSC2)

SPMCSC2 register contains status and control bits associated with the PMC power down

modes.

Note: User applications not enabling STOP1, i.e. not setting PDC to 1, will result in the

STOP4 mode if the application enables the STOP instruction, and subsequently executes

a STOP instruction.

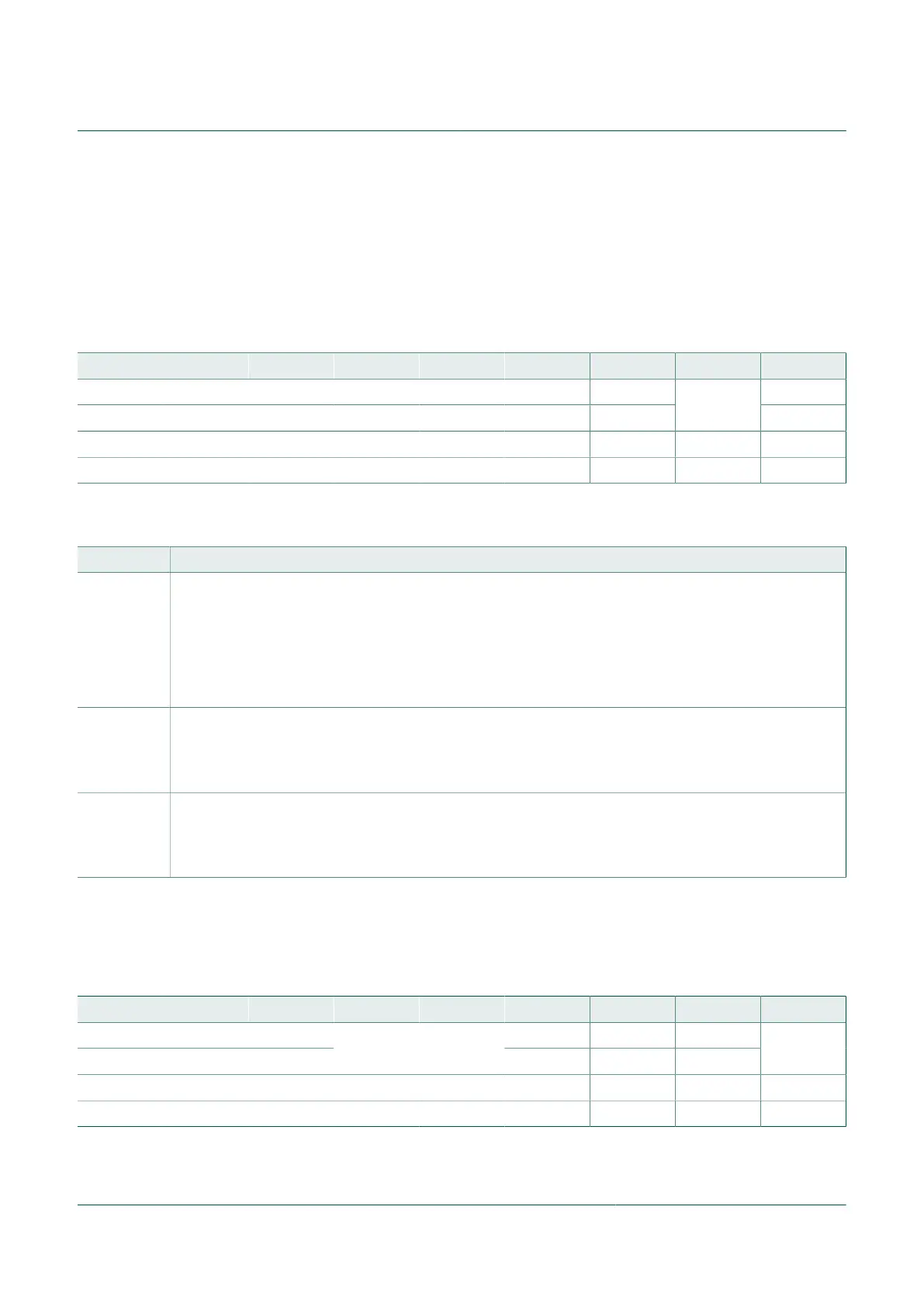

Table 179. PMC status and control 2 register (SPMSC2) (address $180A)

Bit 7 6 5 4 3 2 1 0

R 0 0 0 PDF 0 0 0

W — — — — — PPDACK

PDC

—

Reset 0 0 0 U 0 0 0 0

POR ($00) 0 0 0 0 0 0 0 0

Table 180. SPMSC2 register field descriptions

Field Description

4

PDF

PDF – Power Down Recovery Flag

The PDF bit indicates that the PMC has exited the STOP1 mode. PDF is cleared by writing a 1 to PPDACK.

PDF defaults to 0 following an LVD reset or true POR. True POR is defined as removing and reapplying

power (i.e. both V

DD

and V

DDA

are removed) to the MCU.

0 = Not STOP1 exit; Result of power-on reset; Existing state retained from resets of low voltage detection,

external pin, COP, PWU, illegal opcode, illegal address, soft reset, and back-ground debugger.

1 = STOP1 exit.

2

PPDACK

PPDACK – Partial Power Down Acknowledge control

Writing a logic 1 to PPDACK clears the PDF bit.

0 = Read result; Write no effect; Result of Reset

1 = Write 1 to clear PDF for Power Down acknowledge.

1

PDC

PDC – Power Down Control

The PDC bit controls entry into the STOP1 mode.

0 = Power Down states are disabled; Result of Reset

1 = STOP1 mode enabled.

10.23.3.4 PMC status and control 3 register (PMCSC3)

PMCSC3 register contains status and control bits associated with the PMC Low Voltage

Warning (LVW) subsystem.

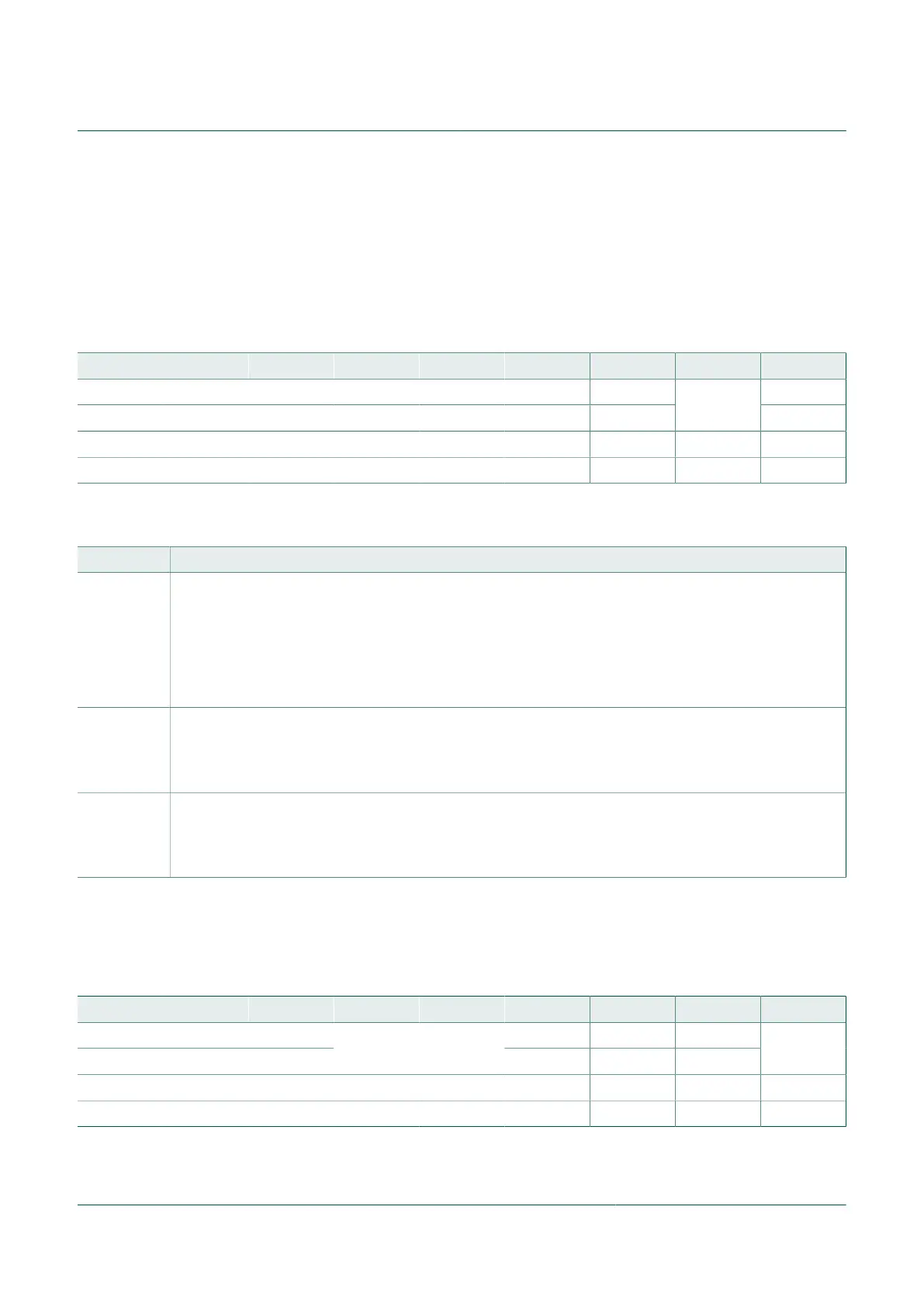

Table 181. PMC status and control 3 register (PMCSC3) (address $180C)

Bit 7 6 5 4 3 2 1 0

R LVWF 0 — 0 0

W — LVWACK

LVDV LVWV

— — —

—

Reset U U U U U U U U

POR ($00) 0 0 0 0 0 0 0 0

Loading...

Loading...