NXP Semiconductors

UM11227

NTM88 family of tire pressure monitor sensors

UM11227 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2020. All rights reserved.

User manual Rev. 6 — 24 April 2020

51 / 205

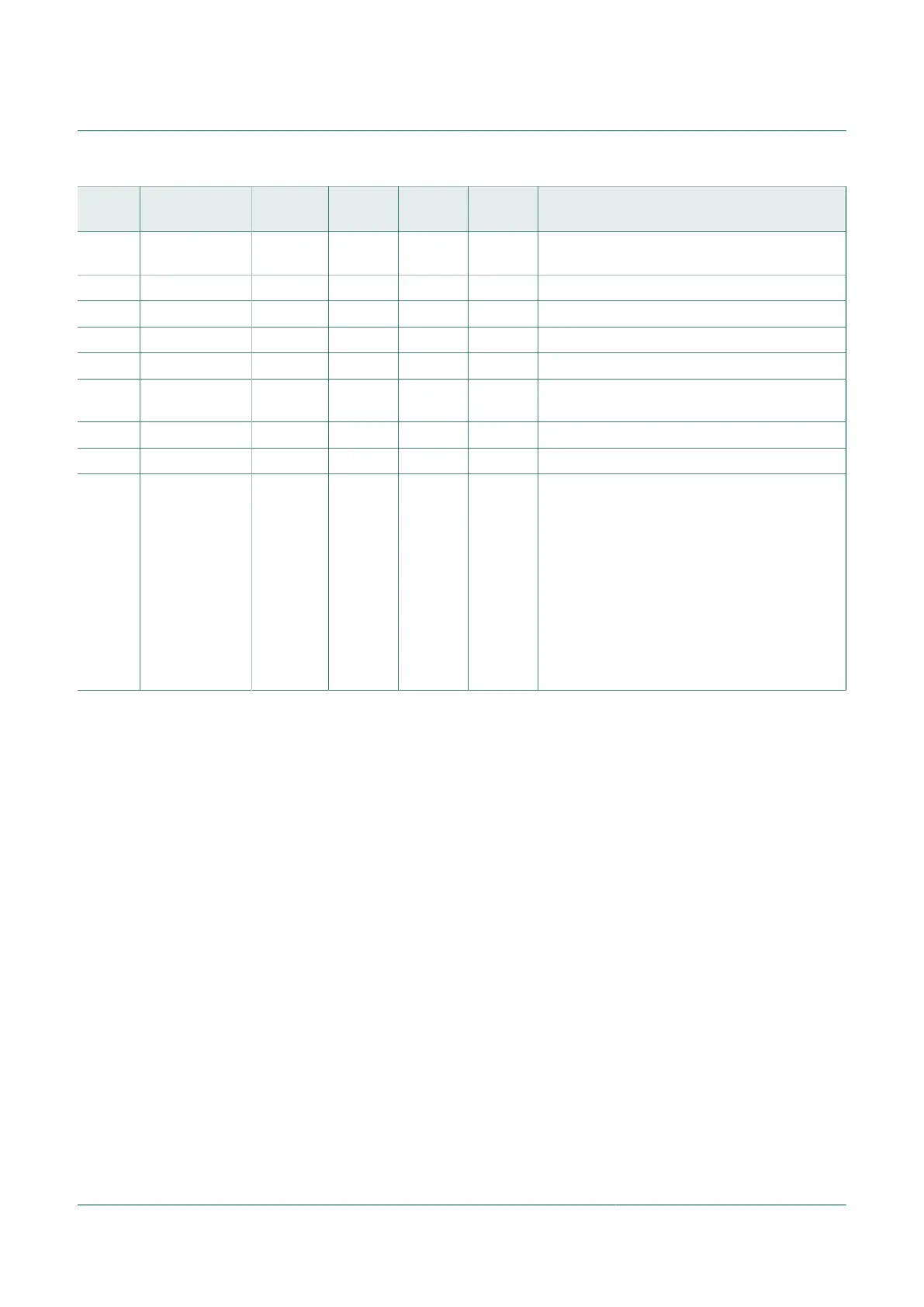

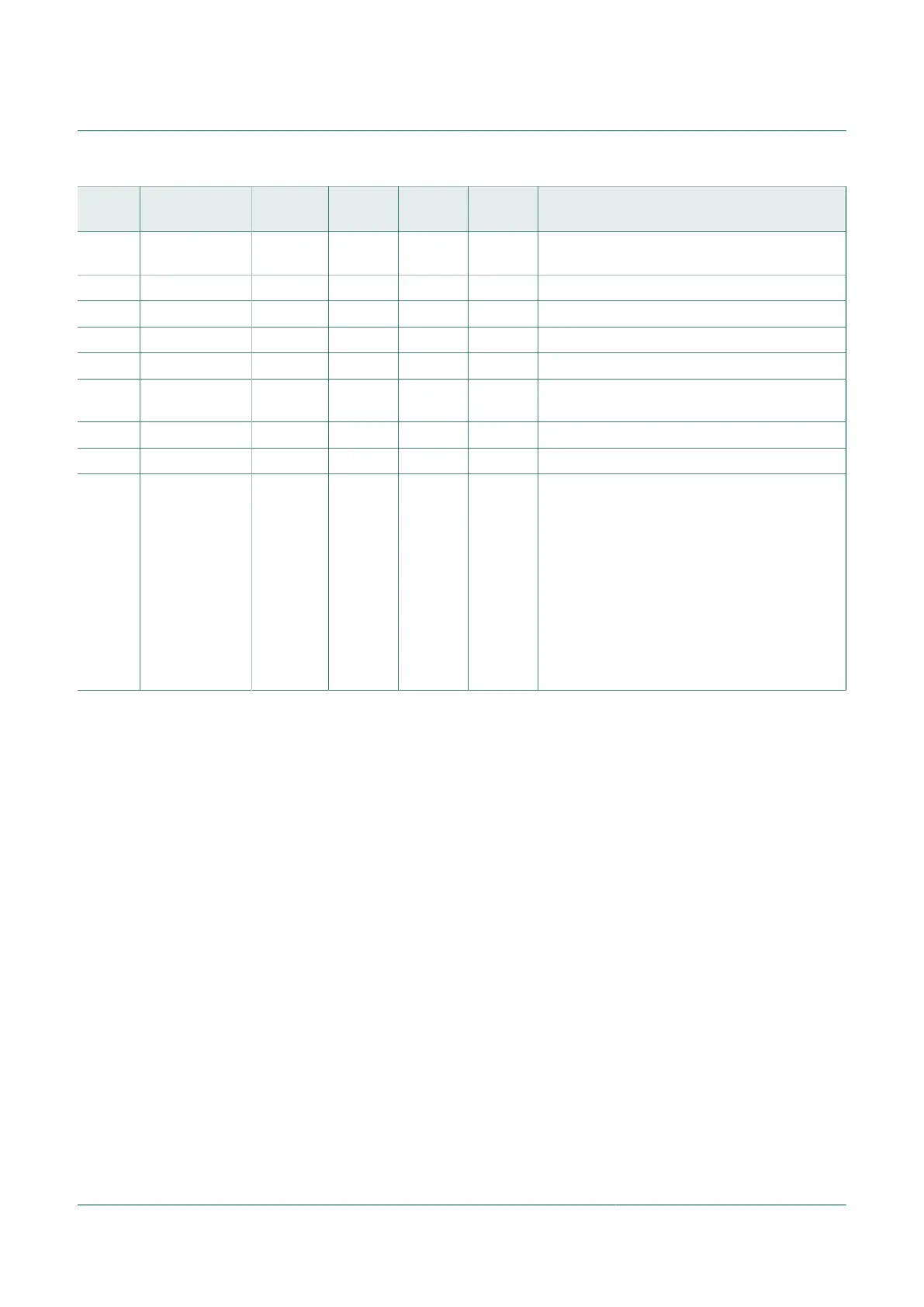

Vector

priority

Hardware

address

Vector

name

Module

source

Flag

name

Enable

name

Description

8 $FFEE - $FFEF Vsmi SMI SMIF SMIIE Sensor Measurement Interface sequence

completed

7 $FFF0 - $FFF1 Vtpm1ovf TPM TOF TOIE TPM timer overflow

6 $FFF2 - $FFF3 Vtpm1ch1 TPM CH1F CH1IE TPM channel 1 event occurrence

5 $FFF4 - $FFF5 Vtpm1ch0 TPM CH0F CH0IE TPM channel 0 event occurrence

4 $FFF6 - $FFF7 Vwuktmr PWU WUF WUT[7:0] PWU wake-up timer interval elapsed

3 $FFF8 - $FFF9 Vlvd PMC LVDF LVDIE PMC supply below LVD warning threshold

detection

2 $FFFA - $FFFB Virq IRQ IRQF IRQE External PTA0 pin edge / level applied

1 $FFFC - $FFFD Vswi CPU — — SWI instruction executed

0 $FFF E- $FFFF Vreset SIM

SIM

SIM

SIM

SIM

SIM

SIM

PMC

PWU

POR

PIN

COP

ILOP

ILAD

PWU

SOFT

LVR

PRF

—

—

COPE

—

—

—

—

LVDRE

PRST[7:

0]

Power-On Reset (POR) initialization sequence

completed

External RST _B pin falling edge applied

COP watchdog timer expired without service

Illegal opcode detected

Illegal address detected

PWU reset initialization sequence completed

Soft reset detected

PMC supply below LVR reset threshold

detection

PWU reset interval timer expired

10.4 Low-Voltage Detect (LVD) System

The NTM88 includes a system to detect low voltage conditions in order to protect

memory contents and control MCU system states during supply voltage variations. The

system is comprised of a power-on reset (POR) circuit and an LVD circuit with a user

selectable trip voltage, either high (V

LVDH

) or low (V

LVDL

). The LVD circuit is enabled

when LVDE in SPMSC1 is high and the trip voltage is selected by LVDV in SPMSC3.

The LVD is disabled upon entering any of the STOP modes unless the LVDSE bit is set.

If LVDSE and LVDE are both set, then the MCU cannot enter STOP1.

10.4.1 Power-on reset operation

When power is initially applied to the NTM88, or when the supply voltage drops below

the V

POR

level, the POR circuit causes a reset condition. As the supply voltage rises, the

LVD circuit holds the chip in reset until the supply has risen above the level determined

by LVDV bit. Both the POR bit and the LVD bit in SRS are set following a POR.

10.4.2 LVD reset operation

The LVD can be configured to generate a reset upon detection of a low voltage condition

has occurred by setting LVDRE to 1 when the supply voltage has fallen below the level

determined by LVDV bit. After an LVD reset has occurred, the LVD system will hold the

NTM88 in reset until the supply voltage has risen above the level determined by LVDV

bit. The threshold for falling and rising differ by a small amount of hysteresis. The LVD bit

in the SRS register is set following either an LVD reset or POR.

Loading...

Loading...