NXP Semiconductors

UM11227

NTM88 family of tire pressure monitor sensors

UM11227 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2020. All rights reserved.

User manual Rev. 6 — 24 April 2020

146 / 205

The ISD and SP intervals can be modified between two consecutive reads, but it must be

done immediately after the MCU wakes-up from the ADC interruption.

To go out the Low Power Direct Mode, immediately after the MCU wakes-up, the user

software low power direct mode routine must reset the SMIEN bit, and then reset the

LPDM bit on two consecutive writes. The SCAP bit will be automatically cleared when

LPDM bit goes low.

After attending to the ADC interrupts, the MCU is allowed to go to STOP4.

10.19.2 SMI register descriptions

10.19.2.1 SMI status and control register (SMICS)

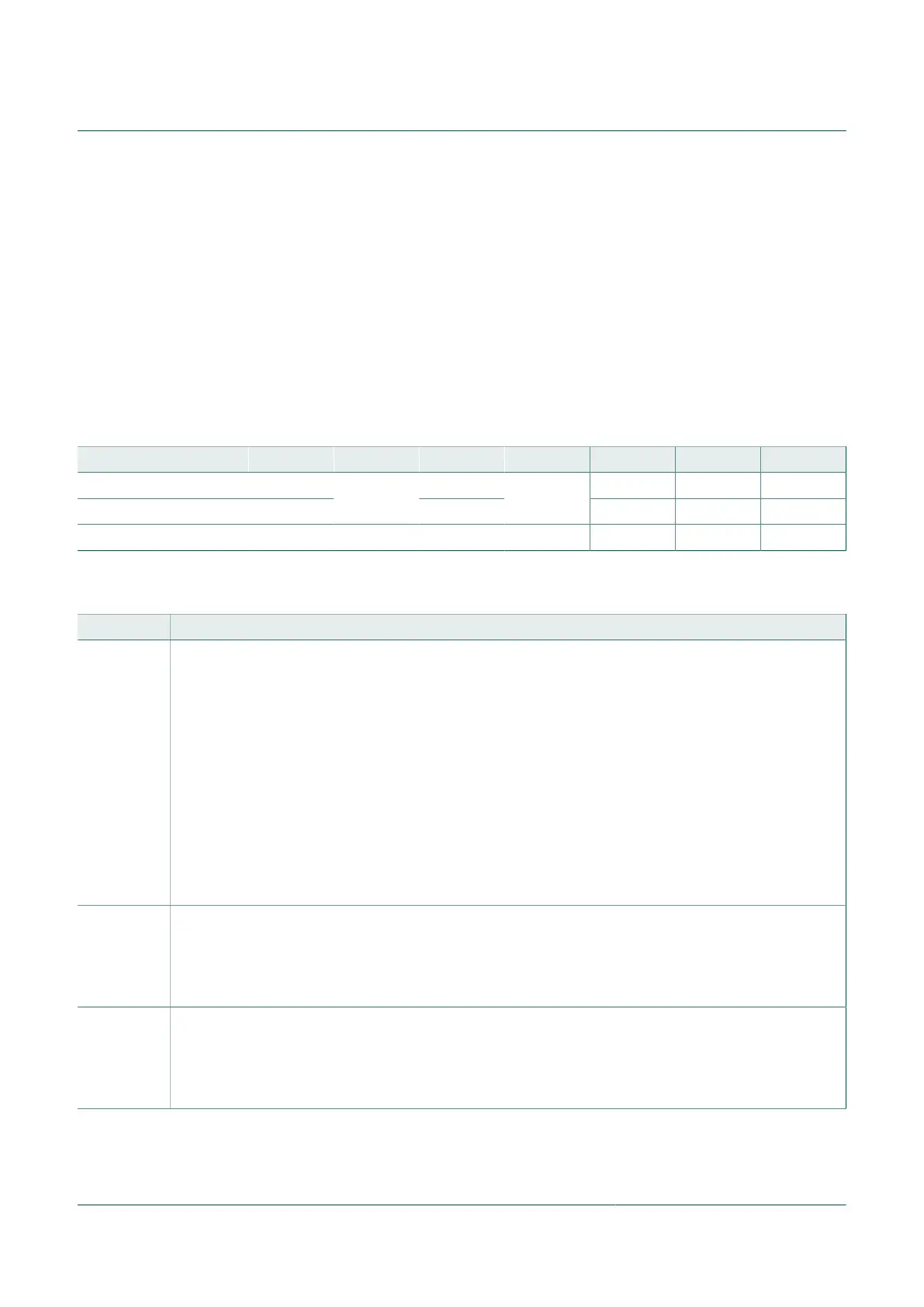

Table 146. SMI status and control register (SMICS) (address $0040)

Bit 7 6 5 4 3 2 1 0

R SMIF 0 SEN 0 0 0

W — SMIFAK

SMIIE

1

LPDM

— — —

Reset ($00) 0 0 0 0 0 0 0 0

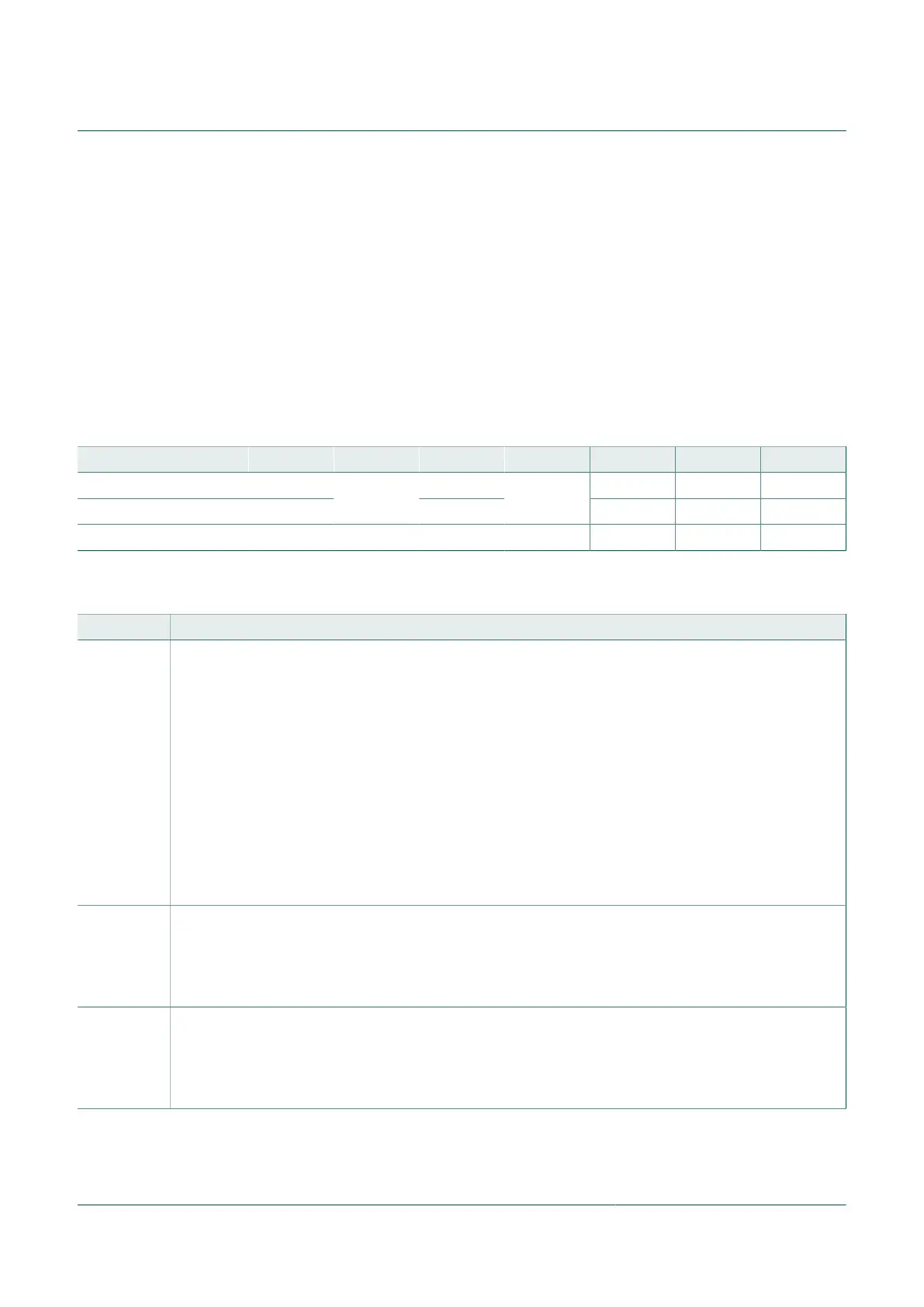

Table 147. SMICS register field descriptions

Field Description

7

SMIF

SMIF — SMI Interrupt Flag

The SMIF bit indicates when an interrupt has been generated by the SMI at the end of the settling delay,

either initial or subsequent only when all of the following conditions exist:

• In the MCU run mode and

• SMI interrupt enable is enabled (set to 1) and

• The SMI low power direct mode is full (set to 0)

This bit is cleared by writing a one to the SMIFAK bit.

0 = SMI interrupt not generated or previously acknowledged; Result of Reset

1 = SMI interrupt generated

Note: Since the SMI Interrupt function is disabled if the MCU is in a Stop mode, or if the Low Power

Direct Mode is enabled, users should avoid using the SMI Interrupt function, and instead rely on the ADC

COCO function to signify completion of the measurement. Enabling the SMI Interrupt functions will induce

unwanted noise or offset into the measurements, and therefore should be avoided in cases where the

highest accuracy is needed.

6

SMIFAK

SMIFAK — Acknowledge SMIF Interrupt Flag

The SMIFAK bit clears the SMIF bit if written with a one. Writing a zero to the SMIFAK bit has no effect on

the SMIF bit. Reading the SMIFAK bit returns a zero. Reset has no effect on this bit.

0 = No effect

1 = Write 1 to clear SMIF for SMI interrupt acknowledge.

5

SMIIE

SMIIE — SMI Interrupt Enable

The SMIIE bit enables the generation of the SMI interrupt when the acquisition cycle is complete. The SMIIE

bit has no effect if the SEN bit is clear.

0 = Disable SMI interrupt; Result of Reset

1 = Enable SMI interrupt if SEN is also = 1.

Loading...

Loading...