NXP Semiconductors

UM11227

NTM88 family of tire pressure monitor sensors

UM11227 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2020. All rights reserved.

User manual Rev. 6 — 24 April 2020

159 / 205

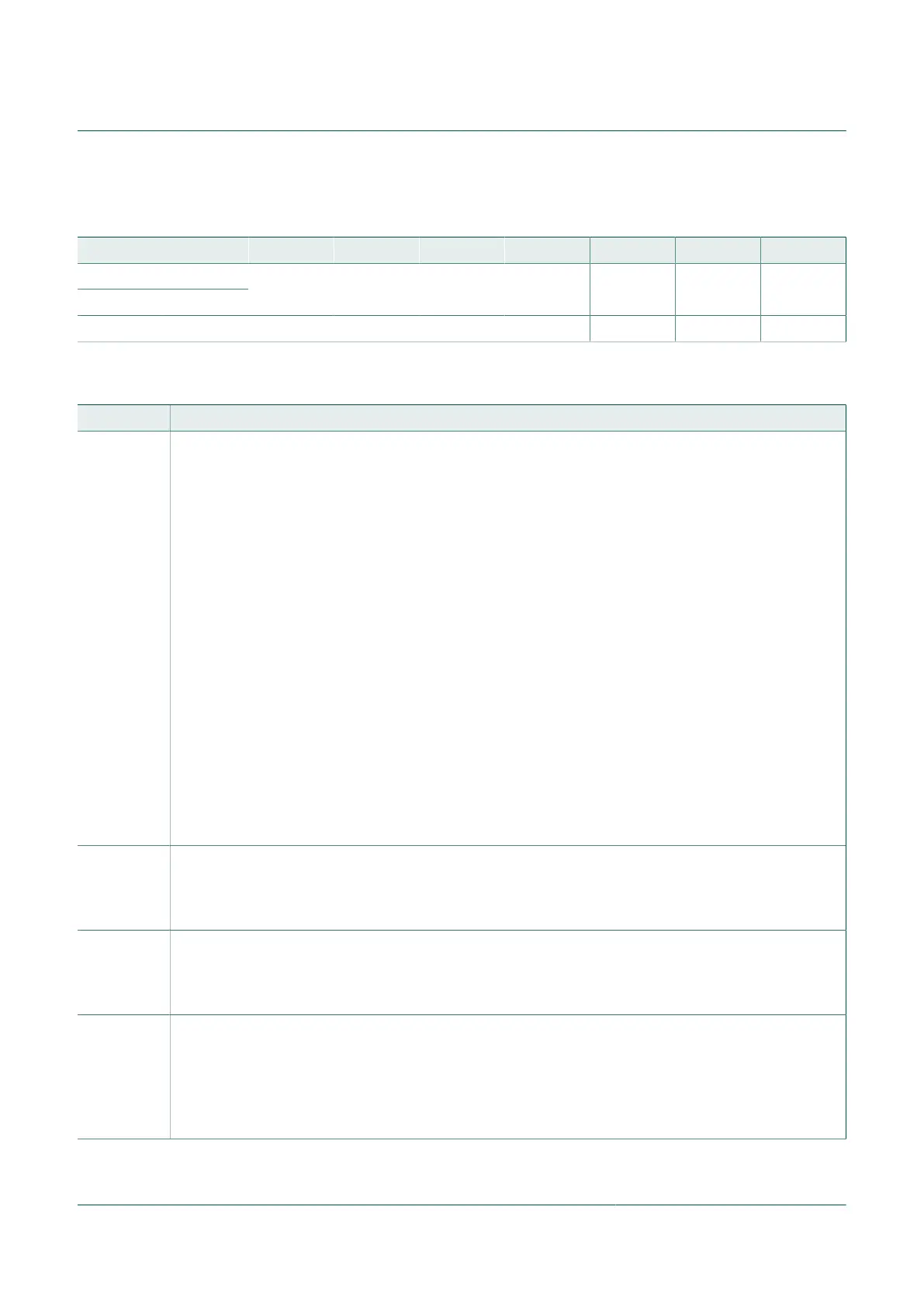

10.22.3.4 SIM option 2 register (SIMOPT2)

Table 166. SIM option 2 register (SIMOPT2) (address $1803)

Bit 7 6 5 4 3 2 1 0

R 0

W —

COPT2 COPT1 COPT0 LFOSEL TCLKDIV BUSCLKS1 BUSCLKS0

Reset ($70) 0 1 1 1 0 0 0 0

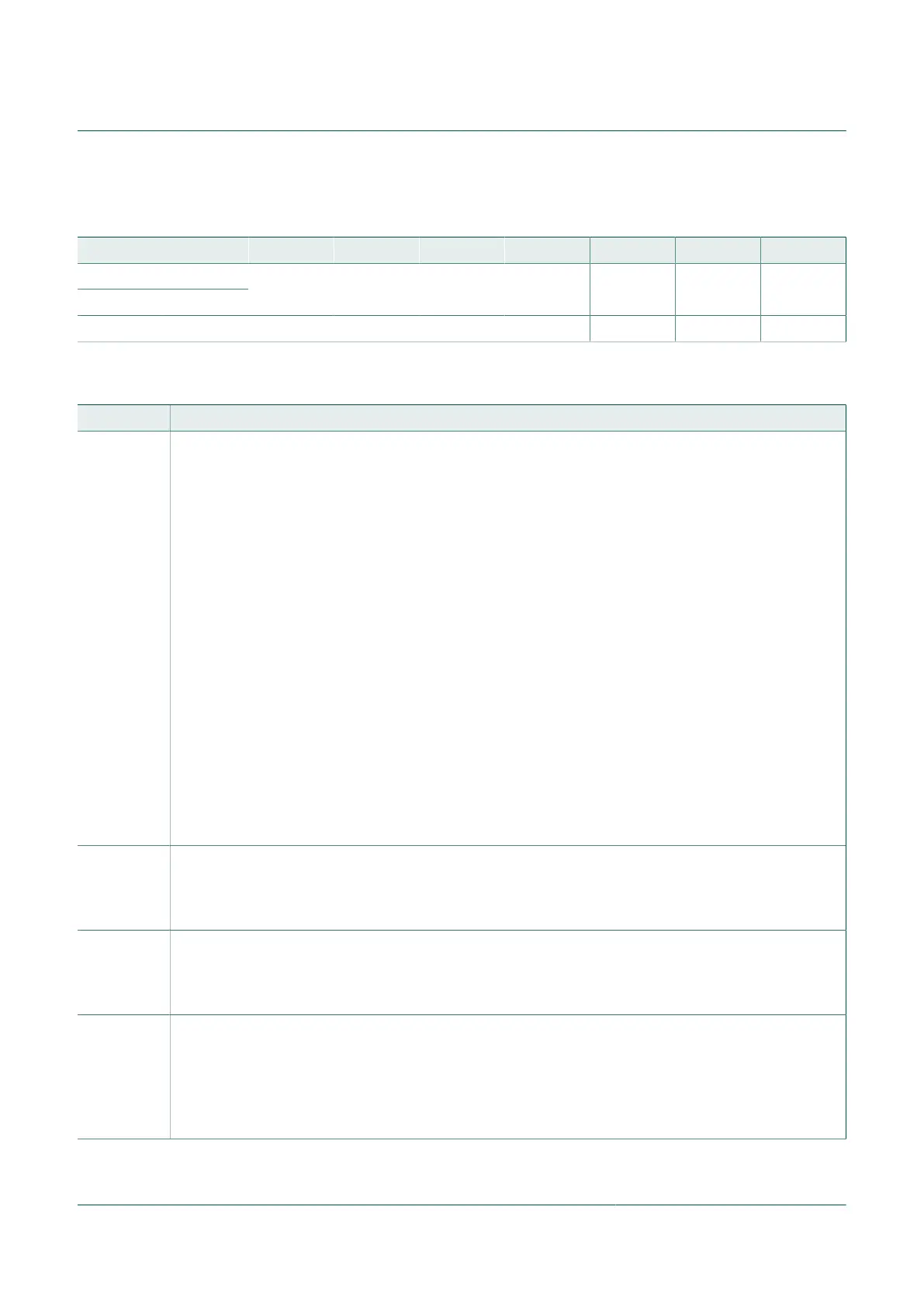

Table 167. SIMOPT2 field descriptions

Field Description

6:4

COPT[2:0]

COPT[2:0] — COP Watchdog Timeout

The 3 bits COPT[2:0] write-once bits, with COPCLKS in SIMOPT1 select the timeout period of the COP.

When COPCLKS = 0 = COP clocked by LFO, ~1 ms COPT[2:0]

0 0 0 = 2

5

LFO bus cycles, ~32 ms

0 0 1 = 2

6

LFO bus cycles, ~64 ms

0 1 0 = 2

7

LFO bus cycles, ~128 ms

0 1 1 = 2

8

LFO bus cycles, ~256 ms

1 0 0 = 2

9

LFO bus cycles, ~512 ms

1 0 1 = 2

10

LFO bus cycles, ~1024 ms

1 1 0 = 2

11

LFO bus cycles, ~2048 ms; Result of Reset

When COPCLKS = 1 = COP clocked by system bus, which is itself selectable at ~2 µs, ~1 µs, ~0.5 µs, and

~0.25 µs.

COPT[2:0]

0 0 0 = 2

13

bus cycles

0 0 1 = 2

14

bus cycles

0 1 0 = 2

15

bus cycles

0 1 1 = 2

16

bus cycles

1 0 0 = 2

17

bus cycles

1 0 1 = 2

18

bus cycles

1 1 0 = 2

19

bus cycles

1 1 1 = 2

19

bus cycles; Result of Reset

3

LFOSEL

LFOSEL — LFO Selected

The LFOSEL selects the TPM channel 0 input to be connected to LFO or to the PTA2

0 = TPM channel 0 input connected to the PTA2; Result of Reset

1 = TPM channel 0 input connected to LFO

2

TCLKDIV

TCLKDIV — TPM External Clock Divider Enable

Enables divider by 8 of DX clock from RF module

0 = TPM External Clock source is the DX clock; Result of Reset

1 = TPM External Clock source is the DX clock divided by 8.

1:0

BUSCL

KS[1:0]

BUSCLKS[1:0] — BUS Clock Divider Selection

The 2 bits BUSCLKS[1:0] select the internal divisions to result in the desired system bus clock:

0 0 = 16 MHz / 2 = Core of 8 MHz and Bus of 4 MHz; Result of Reset

0 1 = 16 MHz / 4 = Core of 4 MHz and Bus of 2 MHz

1 0 = 16 MHz / 8 = Core of 2 MHz and Bus of 1 MHz

1 1 = 16 MHz / 16 = Core of 1 MHz and Bus of 0.5 MHz

Loading...

Loading...