NXP Semiconductors

UM11227

NTM88 family of tire pressure monitor sensors

UM11227 All information provided in this document is subject to legal disclaimers. © NXP B.V. 2020. All rights reserved.

User manual Rev. 6 — 24 April 2020

79 / 205

10.14.1 PWU timer register descriptions

10.14.1.1 Periodic wake-up status and control register (PWUSR)

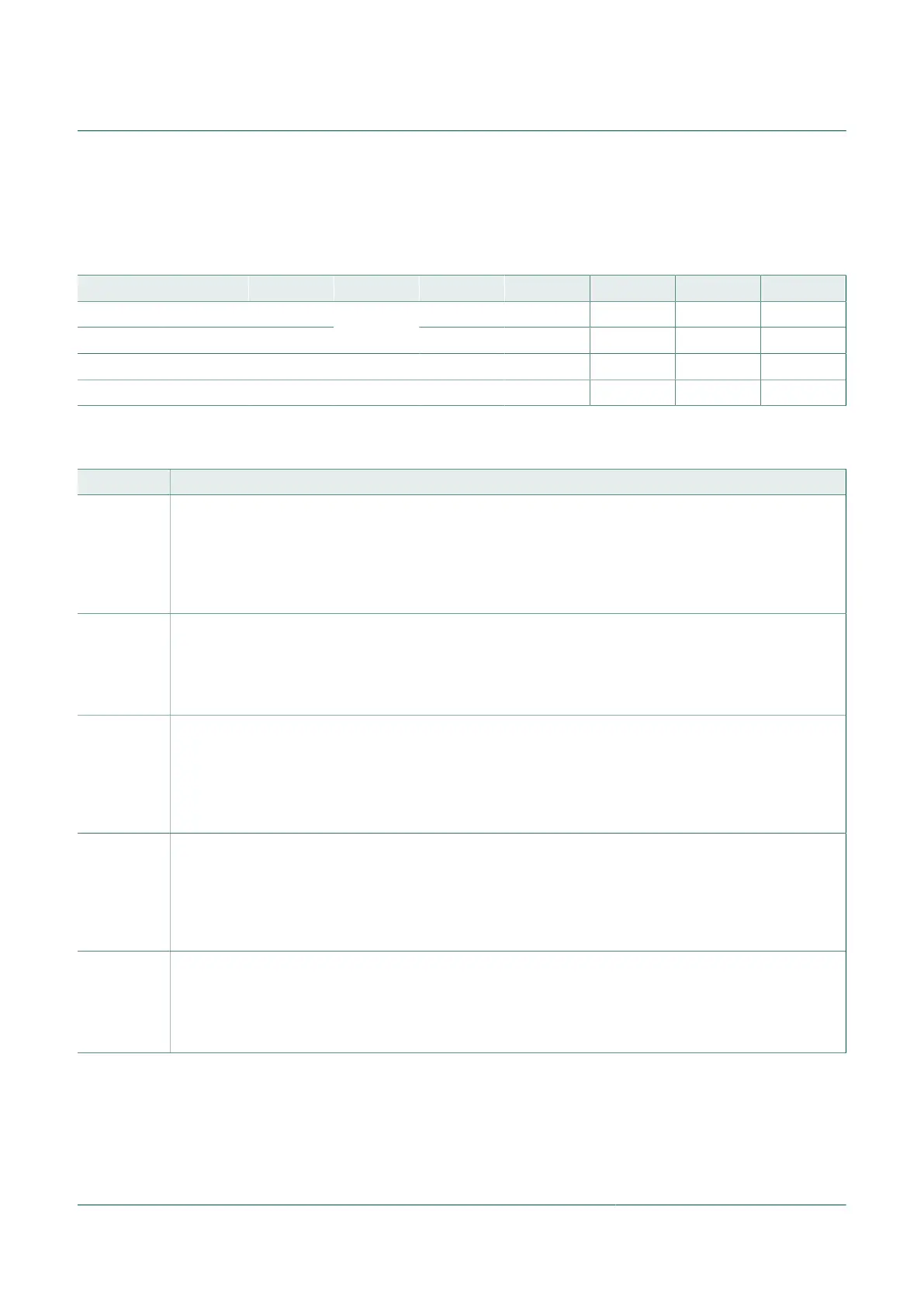

Table 62. Periodic wake-up status and control register (PWUSR) (address $001B)

Bit 7 6 5 4 3 2 1 0

R WUF 0 PRF 0 0 0 0

W — WUFACK

PSEL

— PRFACK — — —

Reset U 0 0 U 0 0 0 0

POR ($00) 0 0 0 0 0 0 0 0

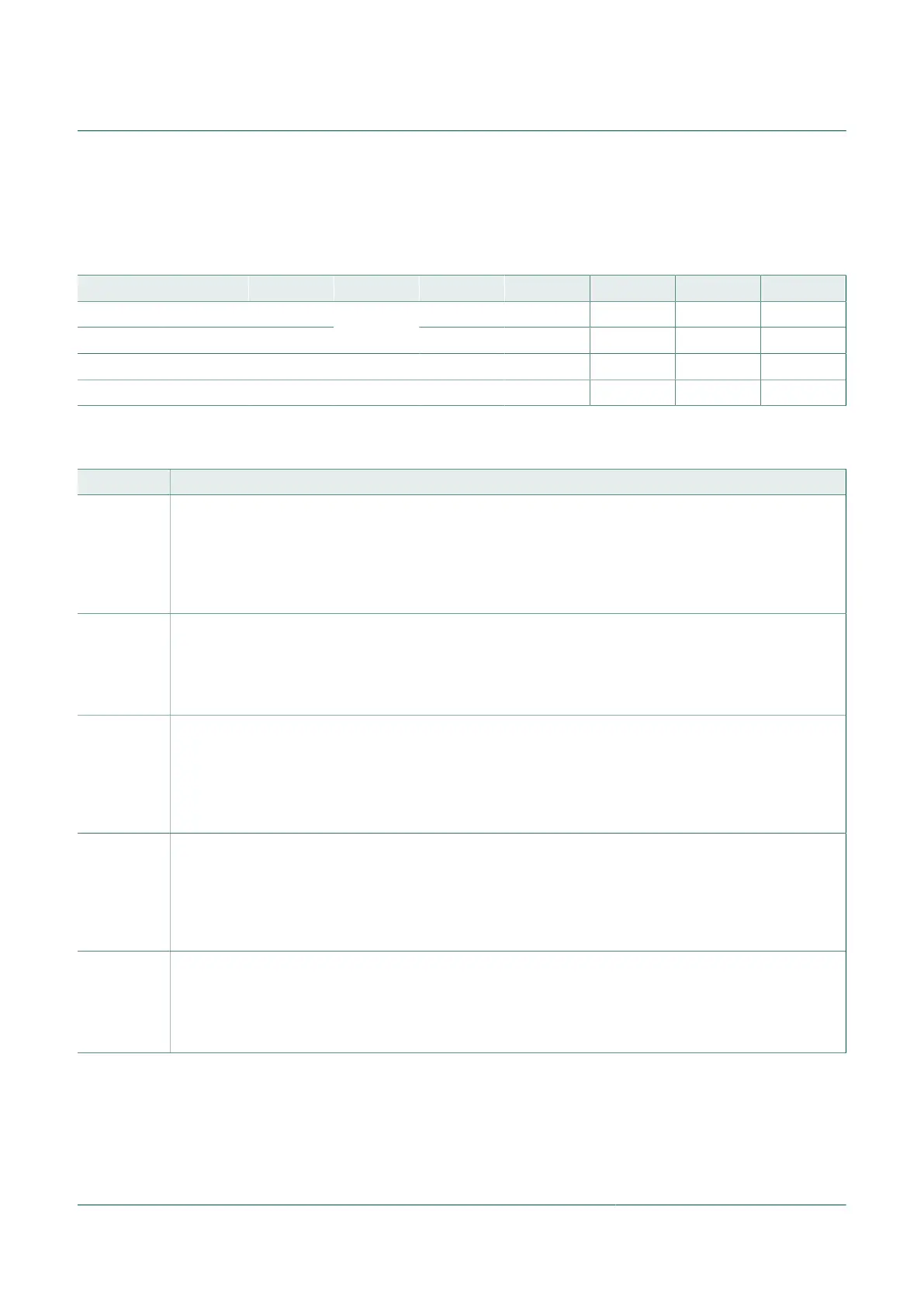

Table 63. PWUSR register field descriptions

Field Description

7

WUF

WUF – Wake-up Interrupt Flag

The read-only WUF bit indicates when a wake-up interrupt has been generated by the PWU. This bit is

cleared by writing a one to the WUFAK bit. Writing a zero to this bit has no effect.

0 = Wake-up interrupt not generated or was previously acknowledged; Result of power-on reset. Existing

state remains after periodic reset.

1 = Wake-up interrupt generated.

6

WUFACK

WUFACK – Wake-up Interrupt Acknowledge

The write-only WUFAK bit clears the WUF bit if written with a one. Writing a zero to the WUFAK bit has no

effect on the WUF bit. Reading the WUFAK bit returns a zero. Reset has no effect on this bit.

0 = Read result; Write no effect; Result of Reset

1 = Write 1 to clear WUF for Wake-up interrupt acknowledge.

5

PSEL

PSEL – Page Select

The PSEL read/write bit selects whether the CSTAT[7:0] register represents the RCLK or PRT counters.

This bit is cleared by a power-on reset that is not created by an exit from the STOP mode, but is unaffected

by other resets.

0 = CSTAT[7:0] represent the RCLK counter status; Result of Reset

1 = CSTAT[7:0] represent the PRT counter status

4

PRF

PRF – Periodic Reset Flag

The read-only PRF bit indicates when a periodic reset has been generated by the PWU. MCU writes to this

bit have no effect. This bit is cleared by writing a one to the PRFAK bit.

0 = Periodic reset not generated or previously acknowledged; Result of power-on reset. Existing state

remains after periodic reset.

1 = Periodic reset generated.

3

PRFACK

PRFACK – PRF Interrupt Acknowledge

The PRFAK bit clears the PRF bit if written with a one. Writing a zero to the PRFAK bit has no effect on the

PRF bit. Reading the PRFAK bit returns a zero.

0 = Read result; Write no effect; Result of Reset

1 = Write 1 to clear PRF for Periodic Reset interrupt acknowledge.

Loading...

Loading...